## University of South Florida Scholar Commons

Graduate Theses and Dissertations

Graduate School

10-17-2003

# Energy and Transient Power Minimization During Behavioral Synthesis

Saraju P. Mohanty University of South Florida

Follow this and additional works at: https://scholarcommons.usf.edu/etd Part of the <u>American Studies Commons</u>

### Scholar Commons Citation

Mohanty, Saraju P., "Energy and Transient Power Minimization During Behavioral Synthesis" (2003). *Graduate Theses and Dissertations.* https://scholarcommons.usf.edu/etd/1431

This Dissertation is brought to you for free and open access by the Graduate School at Scholar Commons. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact scholarcommons@usf.edu.

## Energy and Transient Power Minimization During Behavioral Synthesis

by

Saraju P. Mohanty

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy Department of Computer Science and Engineering College of Engineering University of South Florida

Major Professor: N. Ranganathan, Ph.D. Murali Varanasi, Ph.D. Srinivas Katkoori, Ph.D. Wilfredo A. Moreno, Ph.D. A. N. V. Rao, Ph.D.

> Date of Approval: October 17, 2003

Keywords: peak power, average power, power fluctuation, low power synthesis, datapath scheduling, multiple supply voltages, dynamic frequency clocking, multicycling, digital watermarking

© Copyright 2003, Saraju P. Mohanty

## **DEDICATION**

My state Kalinga (Orissa), World's largest democracy (India), World's oldest democracy (USA), my Parents, my Sisters, Uma, and to every one who has taught me free thinking.

#### ACKNOWLEDGEMENTS

I would like to express gratitude to my major professor, Dr. N. Ranganathan, for his guidance and support throughout my doctoral degree program. I would sincerely like to thank Dr. K. R. Ramakrishan, Dr. Mohan S. Kanakanhalli, Dr. Chitta Baral, Dr. Rabi N. Mahapatra, Dr. Debasmita Misra, Dr. Srinivas Katkoori and Dr. Sanjukta Bhanja for there support in various phases of my student life. Special thanks to Dr. D. Rundus, Dr. R. Perez, Dr. Goldgof and all the members of my Ph.D. committee. I would also like to thank all members of VCAPP group (such as, Ashok, Sunil, Ravi, Karthik, Suvodeep, Mouli, Bamini, Stelian, Hao, Praveen, etc.) for their help and cooperation. Special thanks to Dr. Austell, ISSS office at USF, the office staffs of CSE department at USF and technical support staff of CSE department at USF (Daniel). Last but not the least, I thank all my friends (Uma, Rupesh, Siddy, Ajaya, Lulu, Pati, Prince, Bhabani, Durga, Amaresh, Krishna, Rajib, Sridhar, Saroj, Jai, Hari, etc.), who have always been a constant source of moral support.

## TABLE OF CONTENTS

| LIST OF TABLES                                                                | v    |

|-------------------------------------------------------------------------------|------|

| LIST OF FIGURES                                                               | viii |

| ABSTRACT                                                                      | xiii |

| CHAPTER 1 INTRODUCTION                                                        | 1    |

| 1.1 Fundamentals of High Level Synthesis                                      | 4    |

| 1.1.1 Why High-Level Synthesis ?                                              | 7    |

| 1.1.2 Various Phases of High-Level Synthesis                                  | 8    |

| 1.1.3 A Synthesis Example                                                     | 12   |

| 1.2 Sources of Power Dissipation in a CMOS Circuit                            | 12   |

| 1.3 Methods for Power Reduction in High-Level Synthesis                       | 16   |

| 1.4 Why Peak Power Minimization ?                                             | 18   |

| 1.5 Why Average Power and Energy Reduction ?                                  | 19   |

| 1.6 Why Transient Power Minimization ?                                        | 20   |

| 1.7 Why Frequency and Voltage Scaling ?                                       | 20   |

| 1.8 Multiple Supply Voltages, Dynamic Clocking and Multicycling Preliminaries | 21   |

| 1.8.1 What is Dynamic Frequency Clocking ?                                    | 22   |

| 1.8.2 Energy or Power Reduction Due to Voltage or Frequency Scaling           | 22   |

| 1.8.3 Issues in Multiple Supply Voltage Based Design                          | 25   |

| 1.8.4 Level Converter Design                                                  | 26   |

| 1.8.5 Dynamic Frequency Clocking Unit Design                                  | 27   |

| 1.9 Fundamentals of Digital Watermarking                                      | 31   |

| 1.9.1 General Framework for Watermarking                                      | 32   |

| 1.9.2 Types of Watermarking                                                   | 35   |

| 1.10 Contributions of this Dissertation                                       | 38   |

| 1.11 Dissertation Outline                                                     | 40   |

| CHAPTER 2 RELATED WORK                                                        | 41   |

| 2.1 Datapath Scheduling for Energy or Average Power Reduction using           |      |

| Voltage Reduction                                                             | 42   |

| 2.2 Switching Activity Reduction During High-Level Synthesis                  | 47   |

| 2.3 Datapath Scheduling for Peak Power Reduction                              | 55   |

| 2.4 Scheduling for Variable Voltage Processor                                 | 57   |

| 2.5 Design and Synthesis for Low-Power or High-Performance Variable           |      |

| Voltage / Frequency / Latency and Multiple Voltage Based Systems              | 65   |

i

| 2.6       | Hardware  | e Based Digital Watermarking Systems                                         | 72  |

|-----------|-----------|------------------------------------------------------------------------------|-----|

| 2.7       | This Diss | sertation                                                                    | 73  |

| CHAPTER 3 | B ENER    | RGY MINIMIZATION                                                             | 75  |

| 3.1       | Target Aı | rchitecture and Datapath Specifications                                      | 75  |

| 3.2       | Time Co   | nstrained Scheduling                                                         | 77  |

|           | 3.2.1     | Algorithm Flow                                                               | 78  |

|           | 3.2.2     | Pseudocode Description                                                       | 80  |

|           | 3.2.3     | Time Complexity                                                              | 82  |

| 3.3       | Resource  | Constrained Scheduling                                                       | 84  |

|           | 3.3.1     | Algorithm Flow                                                               | 86  |

|           | 3.3.2     | Pseudocode of the Resource Constrained Algorithm                             | 87  |

|           | 3.3.3     | Time Complexity                                                              | 90  |

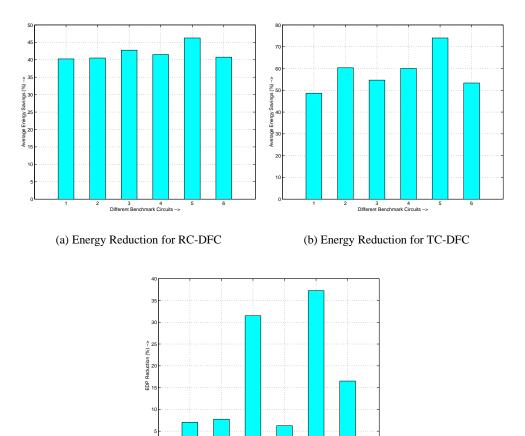

| 3.4       | Experime  | ental Results                                                                | 91  |

| 3.5       | Conclusio | ons                                                                          | 96  |

| CHAPTER 4 | ENER      | RGY DELAY PRODUCT MINIMIZATION                                               | 98  |

| 4.1       | Energy D  | Delay Product of a Datapath Circuit                                          | 98  |

| 4.2       | ILP Form  | nulations                                                                    | 102 |

|           | 4.2.1     | ILP Formulations : Dynamic Frequency Clocking                                | 102 |

|           |           | ILP Formulations : Multicycling                                              | 103 |

| 4.3       | Datapath  | Scheduling Algorithm                                                         | 105 |

|           | 4.3.1     | 8                                                                            | 105 |

|           | 4.3.2     | Scheduling for MVMC                                                          | 106 |

| 4.4       | -         | ental Results                                                                | 110 |

| 4.5       | Conclusio | ons                                                                          | 113 |

| CHAPTER 5 | 5 PEAF    | <b>X POWER AND AVERAGE POWER MINIMIZATION</b>                                | 114 |

| 5.1       | Peak and  | Average Power Consumption of a Datapath Circuit                              | 114 |

| 5.2       | ILP Form  |                                                                              | 117 |

|           | 5.2.1     | ILP Formulations for DFC                                                     | 117 |

|           | 5.2.2     | ILP Formulations for Multicycling                                            | 119 |

| 5.3       |           | ed Scheduler                                                                 | 120 |

|           | 5.3.1     | Scheduler using Multiple Voltages and Dynamic Frequency                      |     |

|           |           | Clocking                                                                     | 121 |

|           | 5.3.2     | Scheduler using Multiple Supply Voltages and Multicycling                    | 124 |

| 5.4       | -         | ental Results                                                                | 126 |

| 5.5       |           | ver Minimization                                                             | 128 |

|           | 5.5.1     | ILP Formulations                                                             | 128 |

|           |           | 5.5.1.1 Multiple Supply Voltages and Dynamic Fre-<br>quency Clocking (MVDFC) | 130 |

|           |           | 5.5.1.2 Multiple Supply Voltages and Multicycling (MVMC)                     | 131 |

|           | 5.5.2     | ILP-Based Scheduler                                                          | 132 |

|           |           | 5.5.2.1 Scheduling for MVDFC                                                 | 132 |

|           |           | 5.5.2.2 Scheduling for MVMC                                                  | 133 |

|           | 5.5.3     | Experimental Results                                                         | 139 |

|           |           | -                                                                            |     |

| 5.6       | Conclusions                                                        | 142 |

|-----------|--------------------------------------------------------------------|-----|

| CHAPTER 6 | ENERGY AND TRANSIENT POWER MINIMIZATION                            | 143 |

| 6.1       | Cycle Power Function (CPF)                                         | 144 |

|           | 6.1.1 Model 1 : CPF using Mean Deviation                           | 145 |

|           | 6.1.2 Model 2 : CPF using Cycle-to-Cycle Gradient                  | 148 |

| 6.2       | CPF-Scheduler Algorithm                                            | 150 |

| 6.3       | Experimental Results                                               | 157 |

| 6.4       | Conclusions                                                        | 164 |

| CHAPTER 7 | TRANSIENT POWER MINIMIZATION                                       | 166 |

| 7.1       | Modified Cycle Power Function                                      | 167 |

| 7.2       | Modeling of Non-linearities                                        | 170 |

|           | 7.2.1 LP Formulation Involving Sum of Absolute Deviations          | 170 |

|           | 7.2.2 LP Formulation Involving Fraction                            | 171 |

| 7.3       | ILP Formulations to Minimize Cycle Power Function                  | 172 |

|           | 7.3.1 Multiple Voltages and Dynamic Frequency Clocking (MVDFC)     | 173 |

|           | 7.3.2 Multiple Voltages and Multicycling (MVMC)                    | 176 |

| 7.4       | ILP-Based Scheduling Algorithm                                     | 179 |

|           | 7.4.1 CPF-MVDFC Scheduling Scheme                                  | 181 |

|           | 7.4.2 CPF-MVMC Scheduling Scheme                                   | 182 |

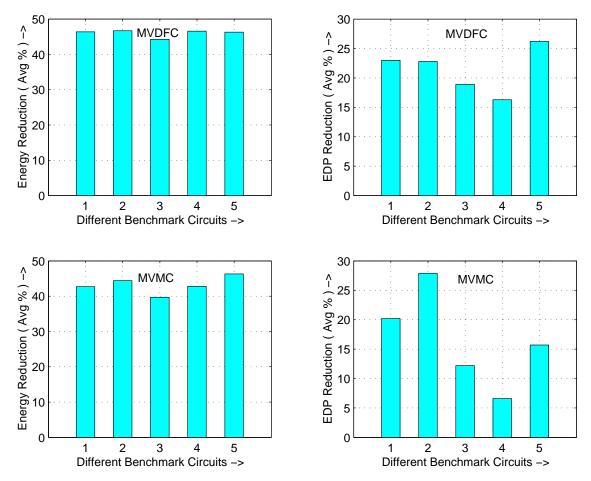

| 7.5       | Experimental Results                                               | 183 |

| 7.6       | Conclusions                                                        | 189 |

| CHAPTER 8 | POWER FLUCTUATION MINIMIZATION                                     | 193 |

| 8.1       | Power Fluctuation Modeling                                         | 194 |

| 8.2       | Modeling of Non-linearities                                        | 197 |

| 8.3       | ILP Formulations to Minimize Mean Power Gradient                   | 199 |

|           | 8.3.1 Formulations using Multiple Voltages and Dynamic Frequency   | 199 |

|           | 8.3.2 Formulations using Multiple Supply Voltages and Multicycling | 201 |

| 8.4       | Scheduling Algorithm                                               | 204 |

| 8.5       | Experimental Results                                               | 207 |

| 8.6       | Conclusions                                                        | 213 |

| CHAPTER 9 | VLSI DESIGN FOR DIGITAL WATERMARKING OF IMAGES                     | 214 |

| 9.1       | Invisible Watermarking in Spatial Domain                           | 214 |

|           | 9.1.1 Spatial Domain Invisible Watermarking Algorithms             | 216 |

|           | 9.1.1.1 Invisible Robust Algorithm                                 | 216 |

|           | 9.1.1.2 Invisible Fragile Algorithm                                | 218 |

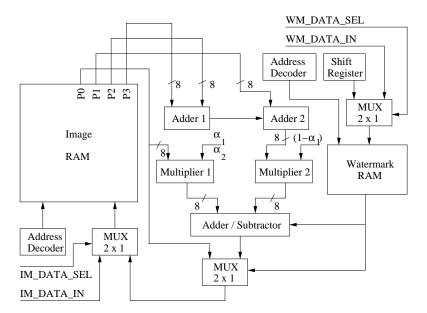

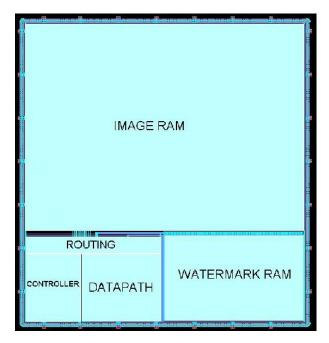

|           | 9.1.2 VLSI Architecture for Invisible Spatial Domain Watermarking  | 220 |

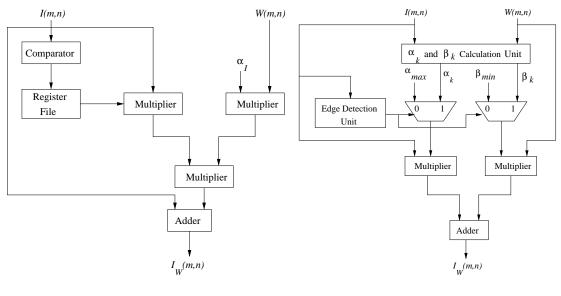

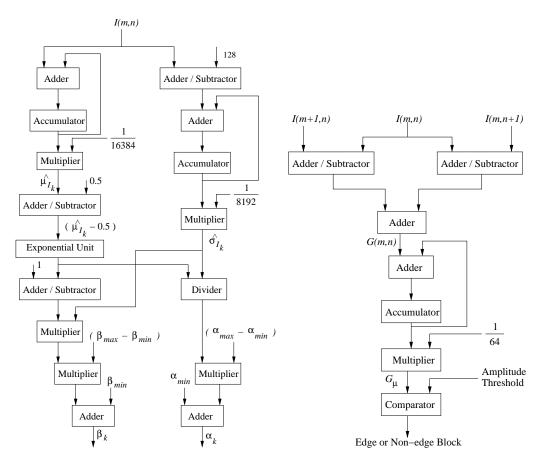

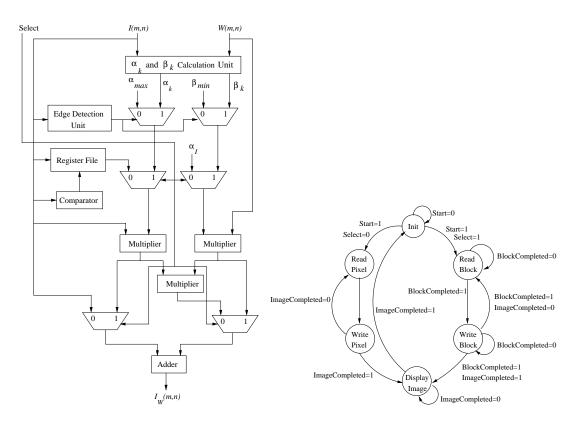

|           | 9.1.2.1 Architecture for Robust Watermarking                       | 220 |

|           | 9.1.2.2 Architecture for Fragile Watermarking                      | 222 |

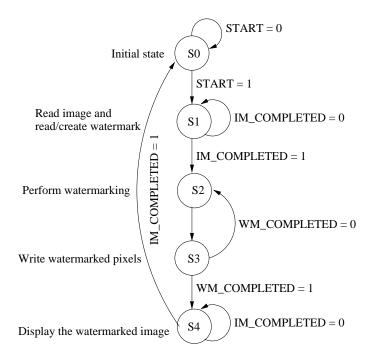

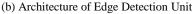

|           | 9.1.2.3 Overall Chip Architecture                                  | 222 |

|           | 9.1.3 Implementation of Spatial Domain Invisible Watermark-        |     |

|           | ing Chip                                                           | 223 |

|           | 9.1.4 Results and Conclusions                                      | 227 |

|           |                                                                    |     |

| 9.2       | Visible V | Vatermarki  | ng in Spatial Domain                                | 229      |

|-----------|-----------|-------------|-----------------------------------------------------|----------|

|           | 9.2.1     | Waterma     | rking Algorithms                                    | 229      |

|           |           | 9.2.1.1     | Visible Watermarking Algorithm 1 :                  | 229      |

|           |           | 9.2.1.2     | Visible Watermarking Algorithm 2 :                  | 231      |

|           | 9.2.2     | VLSI Are    | chitecture                                          | 234      |

|           |           | 9.2.2.1     | Architecture for Algorithm 1 :                      | 234      |

|           |           | 9.2.2.2     | Architecture for Algorithm 2 :                      | 236      |

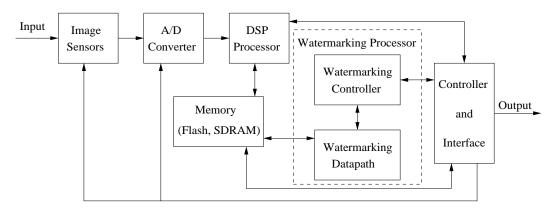

|           |           | 9.2.2.3     | Architecture for the Watermarking Processor :       | 238      |

|           | 9.2.3     | Chip Imp    | lementation                                         | 239      |

|           | 9.2.4     | Results a   | nd Conclusions                                      | 243      |

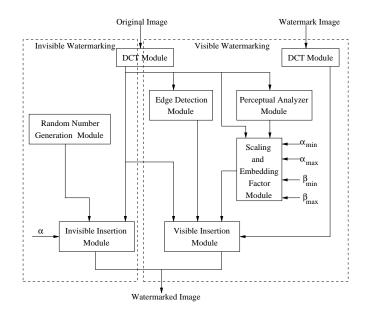

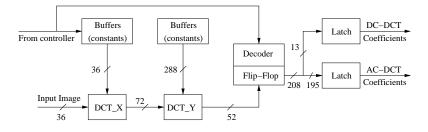

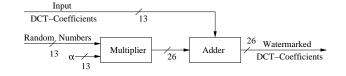

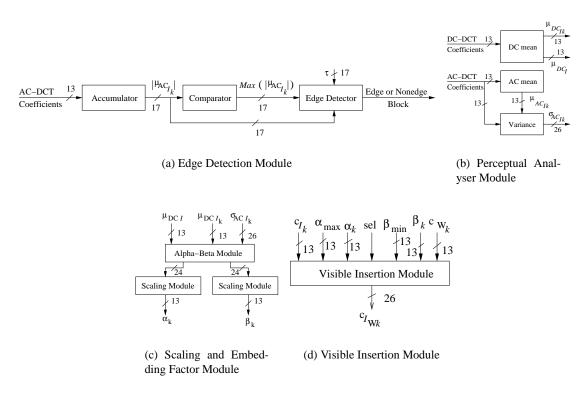

| 9.3       | Invisible | and Visible | e Watermarking in DCT Domain                        | 245      |

|           | 9.3.1     | Waterma     | rking Algorithms                                    | 246      |

|           |           | 9.3.1.1     | Spread Spectrum Invisible Watermarking In-          |          |

|           |           |             | sertion Algorithm                                   | 246      |

|           |           | 9.3.1.2     | Visible Watermarking Insertion Algorithm            | 248      |

|           |           | 9.3.1.3     | Algorithm Modification for Hardware Implementations | s 249    |

|           | 9.3.2     | VLSI Are    | chitecture                                          | 250      |

| CHAPTER 1 | 10 CON    | CLUSION     | S AND FUTURE WORK                                   | 256      |

|           |           |             |                                                     |          |

| REFERENC  | ES        |             |                                                     | 258      |

| ABOUT TH  | E AUTHC   | R           | E                                                   | End Page |

## LIST OF TABLES

| Table 2.1  | Datapath Scheduling Schemes using Multiple Supply Voltages                           | 45 |

|------------|--------------------------------------------------------------------------------------|----|

| Table 2.2  | High-Level Synthesis Schemes using Switching Activity Reduction                      | 51 |

| Table 2.3  | Relative Performance of Various Schemes Proposed for Peak Power<br>Minimization      | 55 |

| Table 2.4  | Scheduling Algorithms for Variable Voltage Processor                                 | 60 |

| Table 2.5  | Design and Synthesis Works on Variable Frequency or Multiple Frequency               | 67 |

| Table 2.6  | Watermarking Chips Proposed in Current Literature                                    | 73 |

| Table 3.1  | List of Functions used in the TC-DFC Algorithm                                       | 79 |

| Table 3.2  | List of Variables and Data Structures used in the TC-DFC Algorithm Description       | 80 |

| Table 3.3  | TC-DFC Frequency Selection : from left $\rightarrow$ right                           | 80 |

| Table 3.4  | Vertex Priority List                                                                 | 80 |

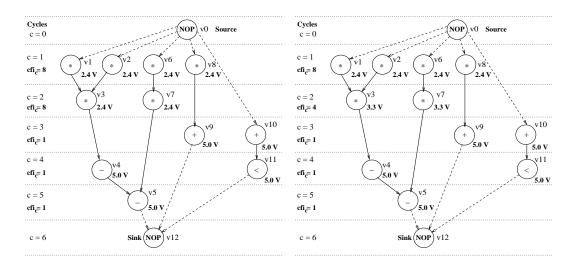

| Table 3.5  | Cycle Priority List : $T_c \approx 2 * T_{cp} or 1.75 * T_{cp}$                      | 82 |

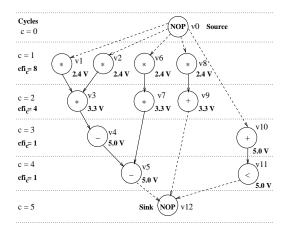

| Table 3.6  | Cycle Priority List : $T_c \approx 1.5 * T_{cp}$                                     | 82 |

| Table 3.7  | Frequency Selection (From Left to Right in Each Step)                                | 85 |

| Table 3.8  | Resource Look-up Table (order, From Left to Right)                                   | 85 |

| Table 3.9  | List of Functions used in the RC-DFC Algorithm                                       | 87 |

| Table 3.10 | List of Variables and Data Structures used in the RC-DFC Algo-<br>rithm Description  | 89 |

| Table 3.11 | Resource Constraints used in our Experiements                                        | 93 |

| Table 3.12 | Energy Details for Different Benchmarks (for $\alpha = 0.5$ ) using RC-DFC Scheduler | 94 |

| Table 3.13 | Configurations for Minimum EDP using RC-DFC                                          | 95 |

| Table 3.14 | Energy Savings using TC-DFC Scheduler                                               | 95  |

|------------|-------------------------------------------------------------------------------------|-----|

| Table 3.15 | Savings for Various Resource Constrained Schedulings                                | 97  |

| Table 3.16 | Savings for Various Time Constrained Schedulings                                    | 97  |

| Table 4.1  | Notations used in Description                                                       | 100 |

| Table 4.2  | Notations used in ILP Formulations                                                  | 102 |

| Table 4.3  | Energy and EDP Estimates for Benchmarks for MVDFC and MVMC Schemes                  | 111 |

| Table 4.4  | Savings for Various Schedulings Schemes                                             | 113 |

| Table 5.1  | Notations used in Description                                                       | 115 |

| Table 5.2  | Notations used in ILP Formulations                                                  | 117 |

| Table 5.3  | Notations used in Expressing Results                                                | 127 |

| Table 5.4  | Resource Constraints used for our Experiement                                       | 128 |

| Table 5.5  | Peak Power, Average Power and PDP Estimates for Benchmarks using Scheduling Schemes | 129 |

| Table 5.6  | Peak and Average Power Reduction for Various Scheduling Schemes                     | 131 |

| Table 5.7  | Resource Constraints used for our Experiment                                        | 139 |

| Table 5.8  | Power Estimates for MVDFC and MVMC Scheduling Schemes                               | 140 |

| Table 5.9  | Power Reduction for Various Scheduling Schemes                                      | 141 |

| Table 6.1  | List of Notataions and Terminology used in CPF Modeling                             | 144 |

| Table 6.2  | Notations used to Express the Results                                               | 158 |

| Table 6.3  | Power Estimates for Different Benchmarks (using Model 1)                            | 159 |

| Table 6.4  | Power Estimates for Different Benchmarks (using Model 2)                            | 163 |

| Table 7.1  | List of Variables used in ILP Formulations                                          | 173 |

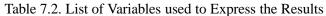

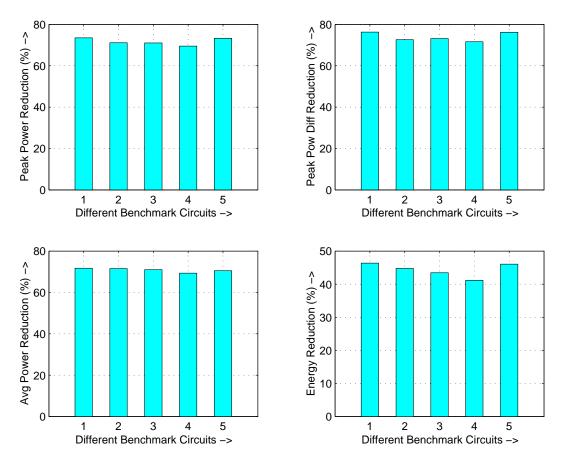

| Table 7.2  | List of Variables used to Express the Results                                       | 184 |

| Table 7.3  | Power, Energy and EDP Estimates for Benchmarks using MVDFC                          | 186 |

| Table 7.4  | Power, energy and EDP Estimates for Benchmarks using MVMC                           | 187 |

| Table 8.1  | Notations used in the Description                                                   | 195 |

| Table 8.2 | Notations used in ILP formulations                               | 199 |

|-----------|------------------------------------------------------------------|-----|

| Table 8.3 | Notations used in Describing the Results                         | 208 |

| Table 8.4 | Power Estimates for Benchmarks                                   | 209 |

| Table 9.1 | Notations used to Explain Spatial Domain Watermarking Algorithms | 216 |

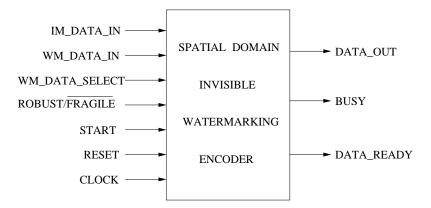

| Table 9.2 | Control Signals for Spatial Domain Invisible Watermarking Chip   | 224 |

| Table 9.3 | Power, Area Details for Individual Units                         | 225 |

| Table 9.4 | Overall Chip Statistics                                          | 226 |

| Table 9.5 | List of Variables used in Algorithm Explanation                  | 230 |

| Table 9.6 | Power and Area of Different Units                                | 242 |

| Table 9.7 | Overall Statistics of the Watermarking Chip                      | 243 |

| Table 9.8 | Notations used in the Description of the Algorithm               | 247 |

| Table 9.9 | Overall Statistics of the DCT Domain Watermarking Chip [85]      | 255 |

vii

## LIST OF FIGURES

| Figure 1.1  | Chronological Change in Power, Power Density, Transistor Count,<br>Gate Count, Operating Frequency and Feature Size of CMOS Inte- |    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------|----|

|             | grated Circuits                                                                                                                   | 2  |

| Figure 1.2  | Desription of Hardware in Different Domains and Abstractions [4]                                                                  | 5  |

| Figure 1.3  | Synthesis Flow                                                                                                                    | 6  |

| Figure 1.4  | Various Phases of High-Level Synthesis                                                                                            | 8  |

| Figure 1.5  | Data Flow Graph and Control Flow Graph of a Square Root Algorithm [3]                                                             | 10 |

| Figure 1.6  | Different Types of Scheduling Algorithms                                                                                          | 11 |

| Figure 1.7  | A Synthesis Example : Step 1 to Step 3                                                                                            | 13 |

| Figure 1.8  | The Synthesis Example : Step 4 to Step 6                                                                                          | 14 |

| Figure 1.9  | Sources of Power Dissipation in a CMOS Circuit                                                                                    | 15 |

| Figure 1.10 | Static Vs Dynamic Power Dissipation for Different Switching Ac-<br>tivity [6, 7]                                                  | 17 |

| Figure 1.11 | Dynamic Frequency Generation using Dynamic Clocking Unit [54]                                                                     | 23 |

| Figure 1.12 | Data Flow Graph in Three Modes of Operation                                                                                       | 24 |

| Figure 1.13 | Level Converter Schematic Diagram [65, 66]                                                                                        | 27 |

| Figure 1.14 | Level Converter Layout and Simulation                                                                                             | 28 |

| Figure 1.15 | Dynamic Clocking Unit : Ranganathan, et. al. [59]                                                                                 | 29 |

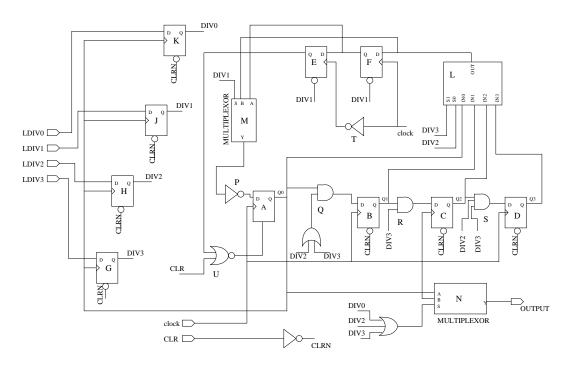

| Figure 1.16 | Dynamic Clocking Unit and Output Clock : Byrnjolfson and Zilic [61]                                                               | 30 |

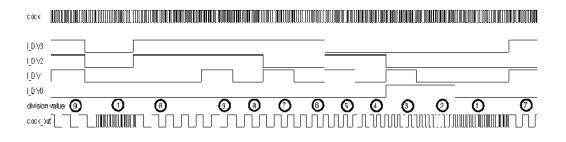

| Figure 1.17 | Visible Watermarked Image [71]                                                                                                    | 32 |

| Figure 1.18 | General Framework of Digital Watermarking                                                                                         | 34 |

| Figure 1.19 | Different Types of Watermarks and Watermarking Techniques                                                                         | 36 |

viii

| Figure 1.20 | Contributions of this Dissertation                                                                          | 38  |

|-------------|-------------------------------------------------------------------------------------------------------------|-----|

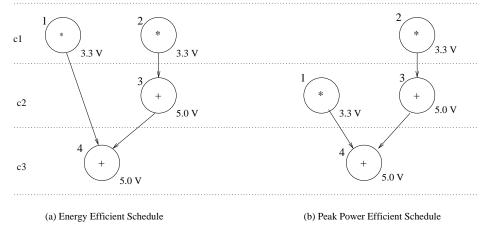

| Figure 1.21 | Energy Vs Peak Power Efficient Schedule                                                                     | 39  |

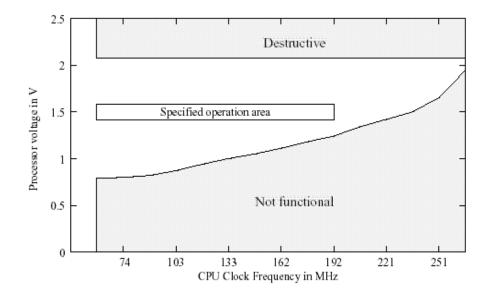

| Figure 2.1  | Variable Voltage Processor Operation : Voltage Vs Frequency [122]                                           | 58  |

| Figure 3.1  | Level Converters Needed for Stepping up Signal                                                              | 76  |

| Figure 3.2  | HAL Differential Equation Solver (with ASAP labels)                                                         | 77  |

| Figure 3.3  | TC-DFC Scheduling Algorithm Flow                                                                            | 78  |

| Figure 3.4  | Pseudo-code for TC-DFC Scheduling Algorithm                                                                 | 81  |

| Figure 3.5  | Schedules Obtained for HAL Benchmark for Different Time Con-<br>straints using TC-DFC                       | 83  |

| Figure 3.6  | RC-DFC Scheduling Algorithm Flow                                                                            | 86  |

| Figure 3.7  | Pseudo-code for RC-DFC Scheduler                                                                            | 88  |

| Figure 3.8  | Final Schedule of FIR Filter DFG (using RC-DFC)                                                             | 91  |

| Figure 3.9  | Average Energy and EDP Reduction for Benchmarks                                                             | 96  |

| Figure 4.1  | ILP Based Scheduling for Low EDP                                                                            | 105 |

| Figure 4.2  | Example Data Flow Graph for Multiple Supply Voltages and Dy-<br>namic Frequency Clocking                    | 106 |

| Figure 4.3  | ILP Formulation for Example DFG for Multiple Supply Voltages and Dynamic Frequency Clocking                 | 107 |

| Figure 4.4  | Example DFG (for RC2) (MVMC)                                                                                | 108 |

| Figure 4.5  | ILP Formulation for Example DFG for Multiple Supply Voltages and Multicycling                               | 109 |

| Figure 4.6  | Reduction for Different Benchmarks Expressed as Percentage in Average                                       | 112 |

| Figure 5.1  | ILP-Based Scheduler                                                                                         | 121 |

| Figure 5.2  | Example DFG for Resource Constraint RC3; using Multiple Sup-<br>ply Voltages and Dynamic Frequency Clocking | 122 |

| Figure 5.3  | ILP Formulation for Example DFG using DFC, for RC3 and Switching Activity $= 0.5$                           | 123 |

| Figure 5.4  | Example DFG for Resource Constraint RC3; using Multiple Sup-<br>ply Voltages and Multicycling               | 124 |

| Figure 5.5  | ILP Formulation for Example DFG using Multicycling, for RC3 and Switching Activity = $0.5$ | 125 |

|-------------|--------------------------------------------------------------------------------------------|-----|

| Figure 5.6  | Average Reduction for Different Bechmarks                                                  | 130 |

| Figure 5.7  | Example DFG (for RC1) (MVDFC)                                                              | 133 |

| Figure 5.8  | ILP Formulation for Example DFG (MVDFC)                                                    | 134 |

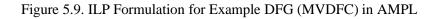

| Figure 5.9  | ILP Formulation for Example DFG (MVDFC) in AMPL                                            | 135 |

| Figure 5.10 | Example DFG (for RC1) (MVMC)                                                               | 136 |

| Figure 5.11 | ILP Formulation for Example DFG (MVMC)                                                     | 137 |

| Figure 5.12 | ILP Formulation for Example DFG (MVMC) in AMPL                                             | 138 |

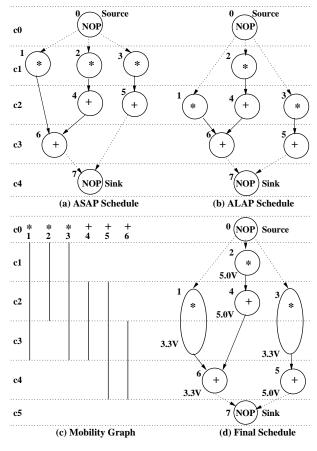

| Figure 5.13 | Average Reductions for Benchmarks                                                          | 141 |

| Figure 6.1  | The CPF-Scheduler Algorithm Flow                                                           | 152 |

| Figure 6.2  | The CPF-Scheduler Algorithm Heuristic                                                      | 153 |

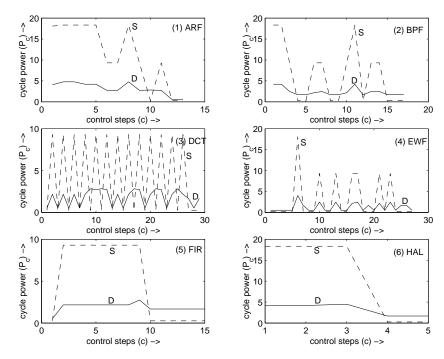

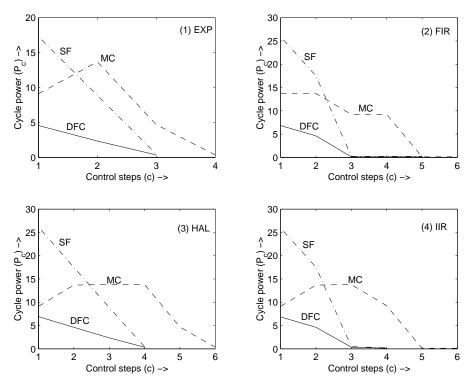

| Figure 6.3  | Cycle Power Consumptions for Resource Constraint RC1                                       | 161 |

| Figure 6.4  | Cycle Power Consumptions for Resource Constraint RC2                                       | 161 |

| Figure 6.5  | Cycle Power Consumptions for Resource Constraint RC3                                       | 162 |

| Figure 6.6  | Cycle Power Consumptions for Resource Constraint RC4                                       | 162 |

| Figure 6.7  | Percentage Average Reduction for Benchmarks using Model1                                   | 164 |

| Figure 6.8  | Percentage Average Reduction for Benchmarks using Model2                                   | 165 |

| Figure 7.1  | Scheduling for $CPF^*$ Minimization                                                        | 180 |

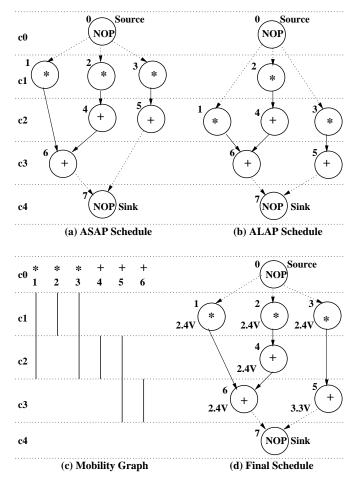

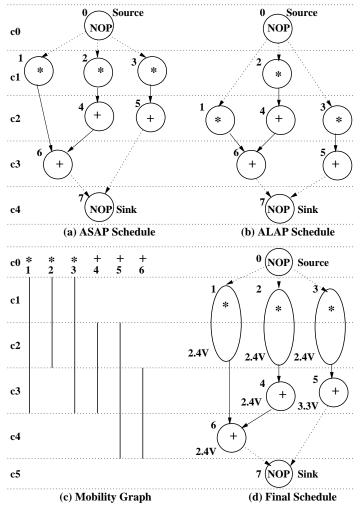

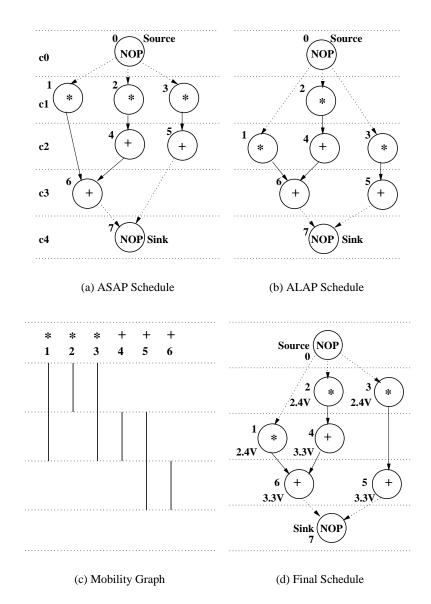

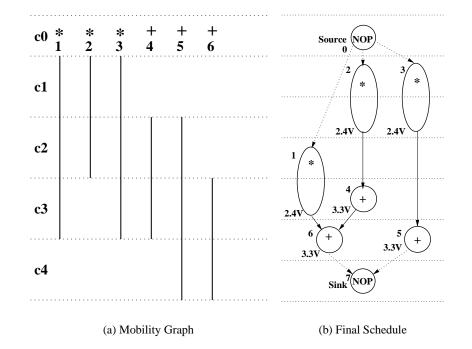

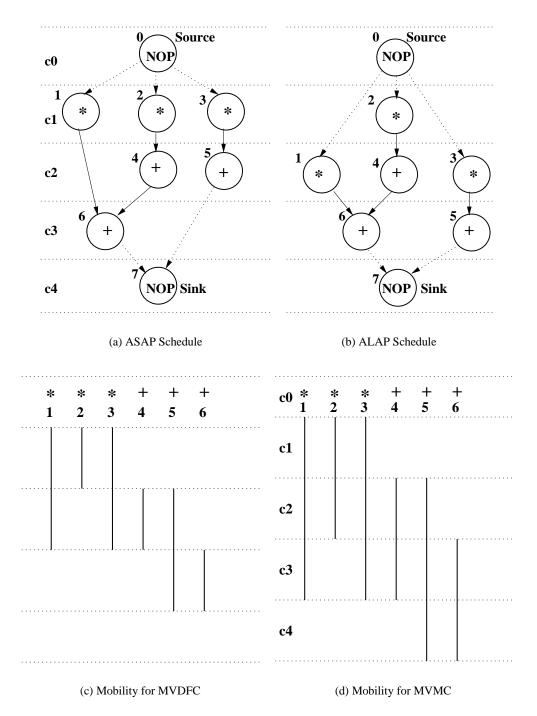

| Figure 7.2  | ASAP and ALAP Schedule for Example DFG (used to find Mobil-<br>ity Graph)                  | 181 |

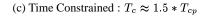

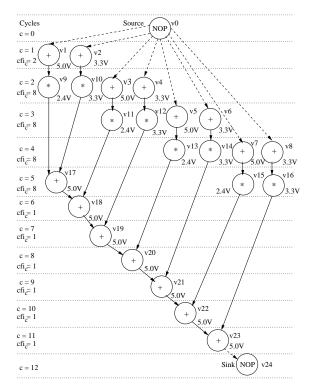

| Figure 7.3  | Mobility Graph and Final Schedule for Example DFG for RC5 us-<br>ing MVDFC                 | 182 |

| Figure 7.4  | Mobility Graph and Final Schedule for Example DFG for RC5 us-<br>ing MVMC                  | 183 |

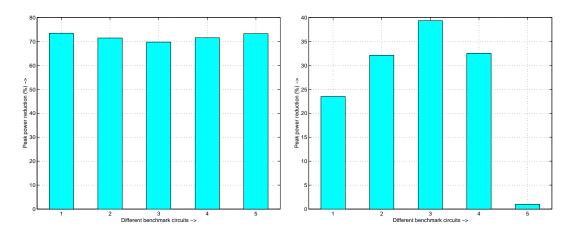

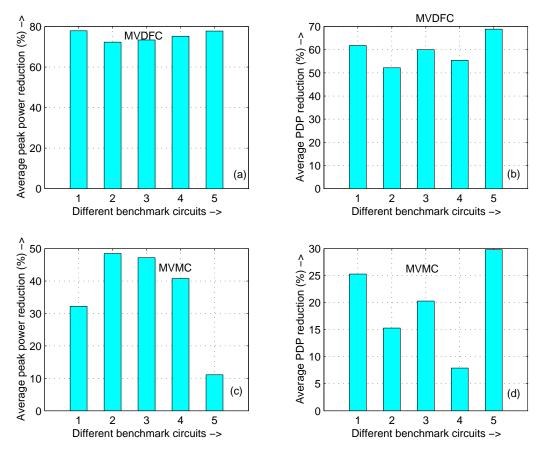

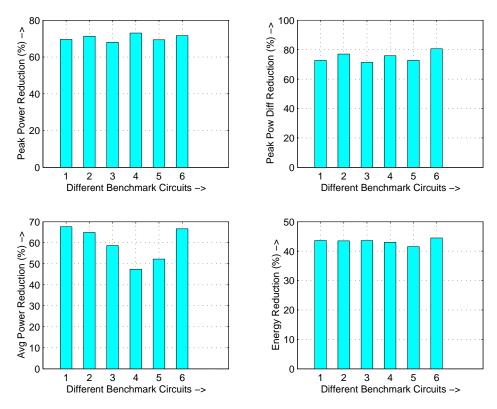

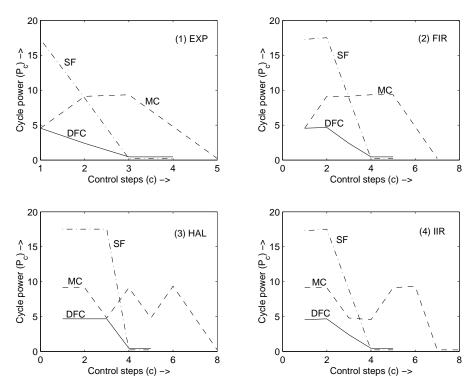

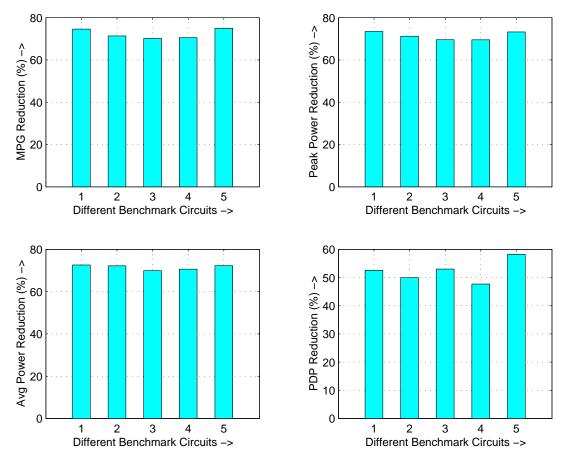

| Figure 7.5  | Average Reductions in Power or Energy for Benchmarks using CPF-<br>MVDFC                   | 188 |

| Figure 7.6  | Average Reductions for Benchmarks using CPF-MVMC                                           | 189 |

|             |                                                                                            |     |

Х

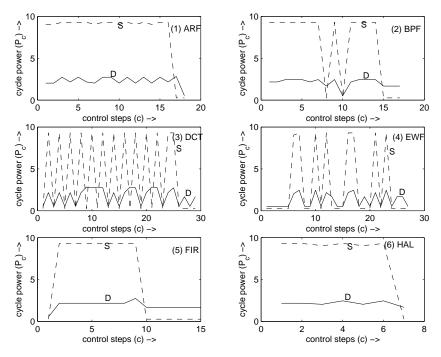

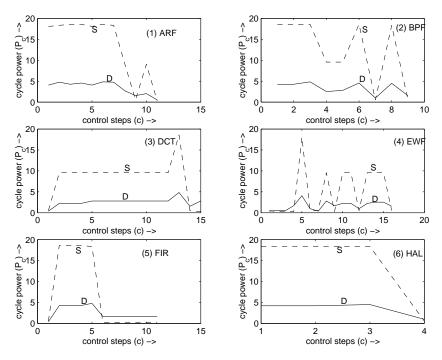

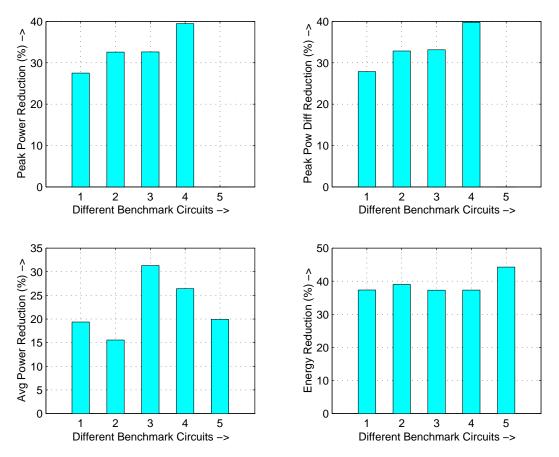

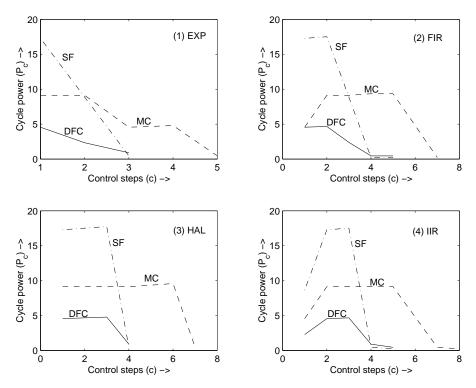

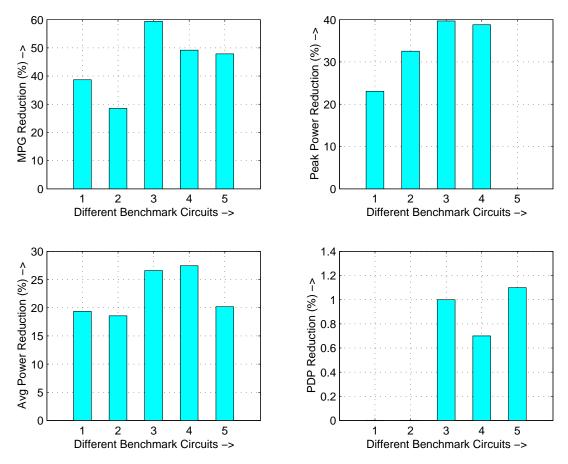

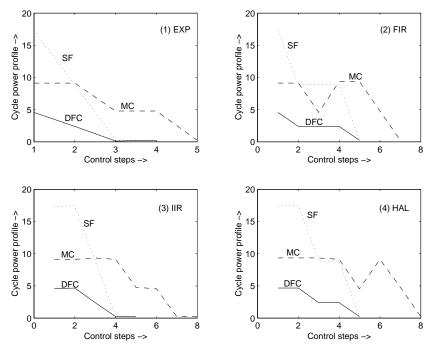

| Figure 7.7  | Power Profile for Benchmark for Resource Constraint RC1                           | 190 |

|-------------|-----------------------------------------------------------------------------------|-----|

| Figure 7.8  | Power Profile for Benchmark for Resource Constraint RC2                           | 191 |

| Figure 7.9  | Power Profile for Benchmark for Resource Constraint RC3                           | 191 |

| Figure 7.10 | Power Profile for Benchmark for Resource Constraint RC4                           | 192 |

| Figure 7.11 | Power Profile for Benchmark for Resource Constraint RC5                           | 192 |

| Figure 8.1  | Scheduling for MPG Minimization                                                   | 205 |

| Figure 8.2  | Example Data Flow Graph (DFG)                                                     | 206 |

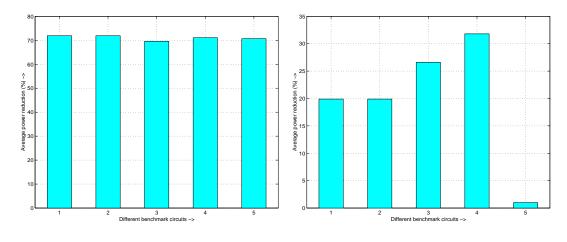

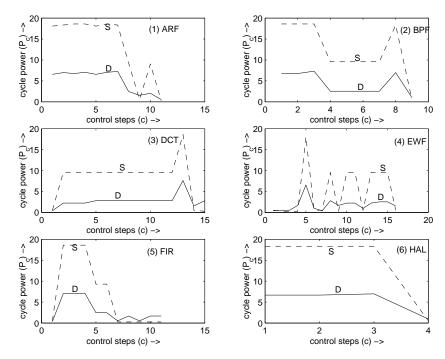

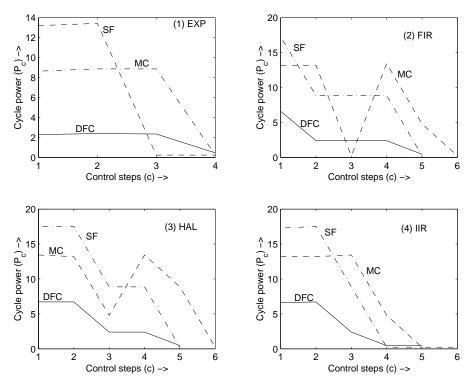

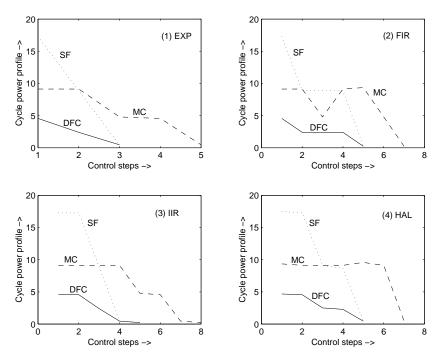

| Figure 8.3  | Average Reductions using DFC Scheme                                               | 210 |

| Figure 8.4  | Average Reductions using Multicycling Scheme                                      | 211 |

| Figure 8.5  | Power Profiles for Benchmarks (for RC2)                                           | 212 |

| Figure 8.6  | Power Profiles for Benchmarks (for RC3)                                           | 212 |

| Figure 8.7  | Power Profiles for Benchmarks (for RC5)                                           | 213 |

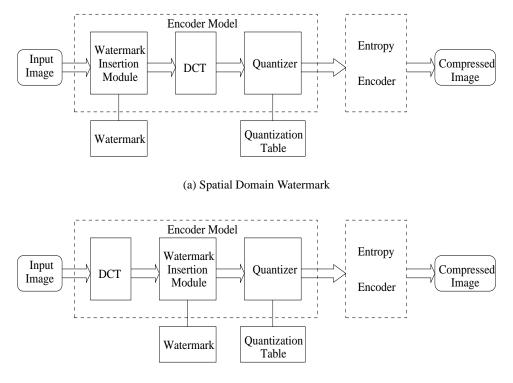

| Figure 9.1  | Secure JPEG Encoder : Block Level View [176]                                      | 215 |

| Figure 9.2  | Secure Digital Still Camera : Schematic View                                      | 215 |

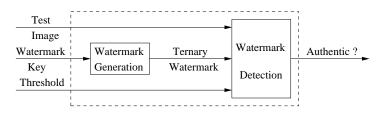

| Figure 9.3  | Invisible Robust Watermarking in Spatial Domain [177, 178]                        | 217 |

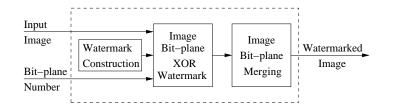

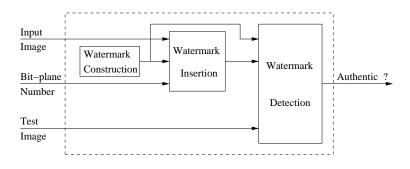

| Figure 9.4  | Invisible Fragile Watermarking in Spatial Domain [83, 72]                         | 219 |

| Figure 9.5  | Datapath for Robust Watermarking                                                  | 220 |

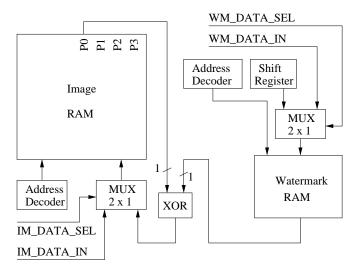

| Figure 9.6  | Datapath for Fragile Watermarking                                                 | 221 |

| Figure 9.7  | Datapath For Combined Spatial Domain Invisible Robust / Fragile<br>Watermarking   | 222 |

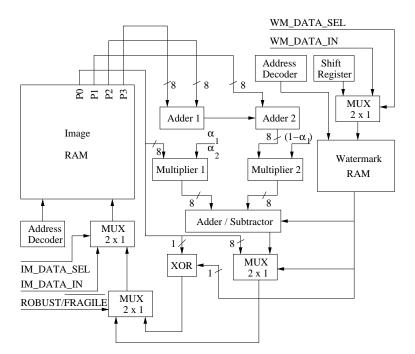

| Figure 9.8  | Controller For Combined Spatial Domain Invisible Robust / Fragile<br>Watermarking | 223 |

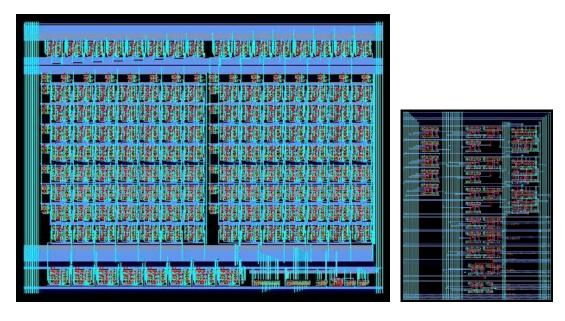

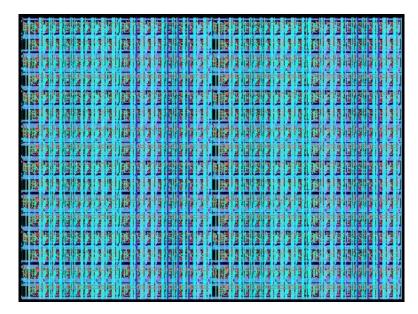

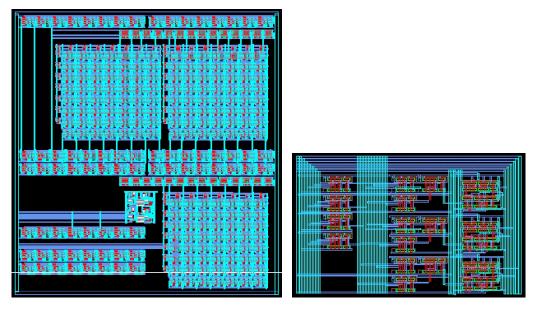

| Figure 9.9  | Layout of the Invisible Spatial Domain Watermarking Datapath and Controller       | 225 |

| Figure 9.10 | Layout of RAM (Zoomed view of a portion is shown)                                 | 226 |

| Figure 9.11 | Layout of the Proposed Spatial Domain Invisible Watermarking Chip                 | 227 |

| Figure 9.12 | Pin Diagram for the Proposed Spatial Domain Invisible Watermark-<br>ing Chip      | 227 |

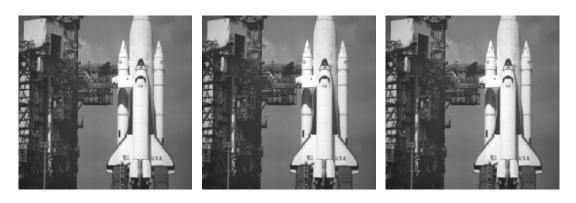

| Figure 9.13 | Spatial Domain Invisible Watermarked Shuttle                                      | 228 |

|-------------|-----------------------------------------------------------------------------------|-----|

| Figure 9.14 | Spatial Domain Invisible Watermarked Bird                                         | 228 |

| Figure 9.15 | Datapath Architectures for the Visible Watermarking Algorithms                    | 235 |

| Figure 9.16 | Individual Datapath Units for Algorithm 2                                         | 237 |

| Figure 9.17 | Architecture for the Proposed Watermarking Processor                              | 239 |

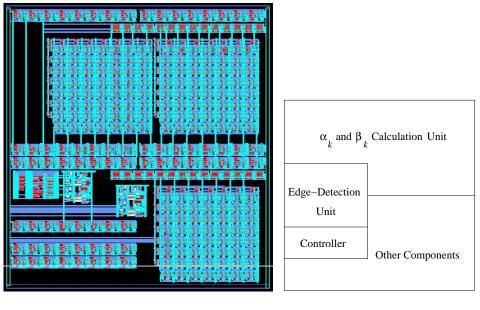

| Figure 9.18 | Layout of Datapath and Controller of the Proposed Chip                            | 241 |

| Figure 9.19 | Layout and Floor Plan of the Proposed Watermarking Chip                           | 242 |

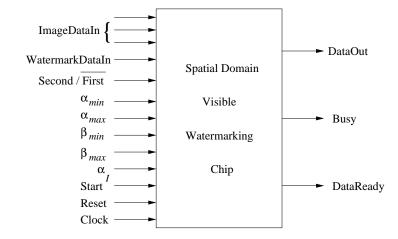

| Figure 9.20 | Pin Diagram for the Proposed Watermarking Chip                                    | 243 |

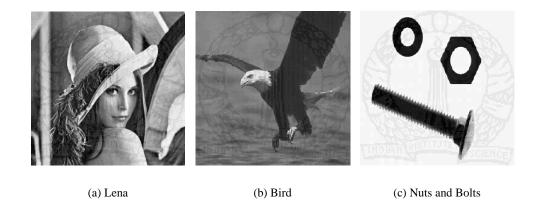

| Figure 9.21 | Original Host Images (a, b, and c) and Watermark Image (d)                        | 244 |

| Figure 9.22 | Watermarked Images for the First Algorithm                                        | 245 |

| Figure 9.23 | Watermarked Images for the Second Algorithm                                       | 245 |

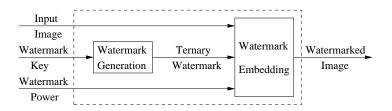

| Figure 9.24 | Combined Architecture for DCT domain Invisible and Visible Wa-<br>termarking Chip | 251 |

| Figure 9.25 | Architecture of the Different Units used for Invisible Watermarking               | 252 |

| Figure 9.26 | Architecture of the Different Units used for Visible Watermarking                 | 253 |

| Figure 9.27 | Dual Voltage and Dual Frequency Operation of the Datapath                         | 254 |

| Figure 9.28 | Layout of the DCT Domain Invisible and Visible Watermarking<br>Chip [85]          | 255 |

| Figure 9.29 | Floorplan of the DCT Domain Invisible and Visible Watermarking<br>Chip [85]       | 255 |

# ENERGY AND TRANSIENT POWER MINIMIZATION DURING BEHAVIORAL SYNTHESIS

#### Saraju P. Mohanty

#### ABSTRACT

The proliferation of portable systems and mobile computing platforms has increased the need for the design of low power consuming integrated circuits. The increase in chip density and clock frequencies due to technology advances has made low power design a critical issue. Low power design is further driven by several other factors such as thermal considerations and environmental concerns. In low-power design for battery driven portable applications, the reduction of peak power, peak power differential, average power and energy are equally important. In this dissertation, we propose a framework for the reduction of these parameters through datapath scheduling at behavioral level. Several ILP based and heuristic based scheduling schemes are developed for datapath synthesis assuming : (i) single supply voltage and single frequency (SVSF), (ii) multiple supply voltages and dynamic frequency clocking (MVDFC), and (iii) multiple supply voltages and multicycling (MVMC). The scheduling schemes attempt to minimize : (i) energy, (ii) energy delay product, (iii) peak power, (iv) simultaneous peak power and average power, (v) simultaneous peak power, average power, peak power differential and energy, and (vi) power fluctuation.

A new parameter called "Cycle Power Function" (CPF) is defined which captures the transient power characteristics as the equally weighted sum of normalized mean cycle power and normalized mean cycle differential power. Minimizing this parameter using multiple supply voltages and dynamic frequency clocking results in the reduction of both energy and transient power. The cycle differential power can be modeled as either the absolute deviation from the average power or as the cycle-to-cycle power gradient. The switching activity information is obtained from behavioral simulations. Power fluctuation is modeled as the cycle-to-cycle power gradient and to reduce fluc-

xiii

tuation the mean power gradient (MPG) is minimized. The power models take into consideration the effect of switching activity on the power consumption of the functional units.

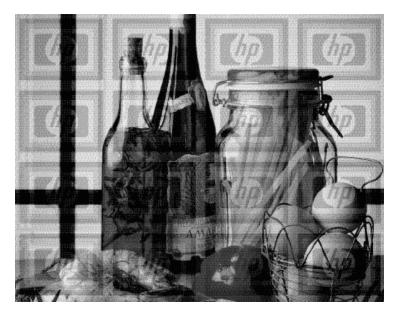

Experimental results for selected high-level synthesis benchmark circuits under different constraints indicate that significant reductions in power, energy and energy delay product can be obtained and that the MVDFC and MVMC schemes yield better power reduction compared to the SVSF scheme. Several application specific VLSI circuits were designed and implemented for digital watermarking of images. Digital watermarking is the process that embeds data called a watermark into a multimedia object such that the watermark can be detected or extracted later to make an assertion about the object. A class of VLSI architectures were proposed for various watermarking algorithms : (i) spatial domain invisible-robust watermarking scheme, (ii) spatial domain invisible-fragile watermarking scheme, (iii) spatial domain visible watermarking scheme, (iv) DCT domain invisible-robust watermarking scheme, and (v) DCT domain visible watermarking scheme. Prototype implementation of (i), (ii) and (iii) are given. The hardware modules can be incorporated in a "JPEG encoder" or in a "digital still camera".

## CHAPTER 1

#### INTRODUCTION

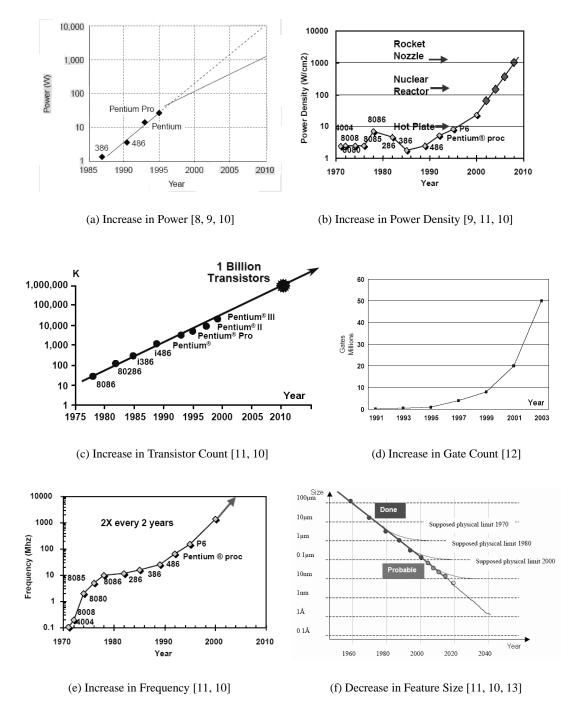

Low power circuit design is a three dimensional problem involving area, performance and power trade-offs. Because of the decreasing feature size and increasing packing density, it may be possible to trade area against power [1]. The trend of decreasing device size and increasing chip densities involving several hundred millions of transistors per chip has resulted in tremendous increase in design complexity. Designing chips of such complexity using traditional *capture and simulate* methodology is time consuming and difficult. The industry has started looking at the development cycle to reduce design time and to gain a competitive edge. High-level synthesis of digital circuits has become necessary due to several advantages such as, reduction of design time, exploration of different design styles, meeting design constraints and requirements [2, 3, 4]. Additionally, this trend of reducing the feature size with increasing the clock frequency has made reliability a big challenge for the designers, mainly because of high on-chip electric fields [1, 5, 6, 7, 8]. Fig. 1.1 shows the chronologcal change in power, power density, transistor count, gate count, operating frequency and feature size of CMOS ICs.

High-level synthesis process can be defined as the translation process from behavioral description to its structural description [3, 14, 4, 15]. This is analogous to a "compiler" that translates a high-level language program in C/Pascal to an assembly language program. High-level synthesis is also known as behavioral-level synthesis or algorithm-level synthesis. The constraints which are to be considered in high-level synthesis are area, performance, power consumption, reliability, testability and cost. With the increasing demand for personal computing devices and wireless communications equipment, the demand for designing low power consuming circuits has increased. "Power" has become an important parameter alongwith area and throughput. The need for low power synthesis is driven by several factors [16, 17, 18, 19, 20]:

1

Figure 1.1. Chronological Change in Power, Power Density, Transistor Count, Gate Count, Operating Frequency and Feature Size of CMOS Integrated Circuits

- Increased demand for portable systems: Emergence of portable devices like laptop computers, mobile phones etc. for which battery life is an important factor

- Thermal considerations: If power dissipation can be reduced, the cost of cooling and packaging would be reduced.

- Environmental concerns: The smaller the power dissipation in a circuit, lesser the heat pumped into the rooms. So, the electricity consumption will be lower and impact on the environment will be less.

- Reliability issues: If the power consumption is higher, the temperature in the circuit is increased. This may lead to phenomenon like electromigration and hot-electron effects. This causes reduction in the reliability of the system. In fact, it is seen that for every  $10^{\circ}C$  rise in operating temperature, roughly doubles the failure rate of the components.

The growth of high speed computer networks and that of the internet, in particular, has explored means of new business, scientific, entertainment, and social opportunities. Ironically, the cause for the growth is also of the apprehension - use of digital formatted data. Digital media offer several distinct advantages over analog media, such as high quality, easy editing, high fidelity copying. The ease by which a digital information can be duplicated and distributed has led to the need for effective copyright protection tools. Various software products have been recently introduced in attempt to address these growing concerns. It is done by hiding metadata (information) within digital audio, images and video files. One way of such data hiding is *digital signature*, *copyright* label or digital watermark, that completely characterizes the person who applies it and, therefore, marks it as being his intellectual property. *Digital Watermarking* is the process that embeds data called a watermark into a multimedia object such that watermark can be detected or extracted later to make an assertion about the object. While the software implementation of digital watermarking techniques are enormously large, the hardware of the same is negligibly small. The hardware implementation has advantages over the software implementation in terms of low power, high performance and reliability. Also, the hardware implementation of watermarking techniques is absolutely essential for real-time watermarking applications, such as of digital TV broadcasting.

This chapter presents a general overview of high-level synthesis and power minimization in VLSI circuits. The chapter is organized as follows. Section 1.1 discusses high-level synthesis in general and motivation behind high level synthesis. The various sources of power consumption are discussed in Section 1.2. The possible methods of power reduction are described in Section 1.3. Section 1.4 discusses why we need to minimize peak power. The need for average power and energy reduction is listed in Section 1.5 and that of transient power is in Section 1.6. Section 1.7 discusses how frequency and voltage scaling can reduce energy / power in a circuit. The fundamentals of digital watermarking is discussed in Section 1.9. The design issues for multiple supply voltage and dynamic frequency clocking based circuits are discussed in Section 1.8. Section 1.10 discusses the contribution of this dissertation. The dissertation outline is given in Section 1.11.

#### 1.1 Fundamentals of High Level Synthesis

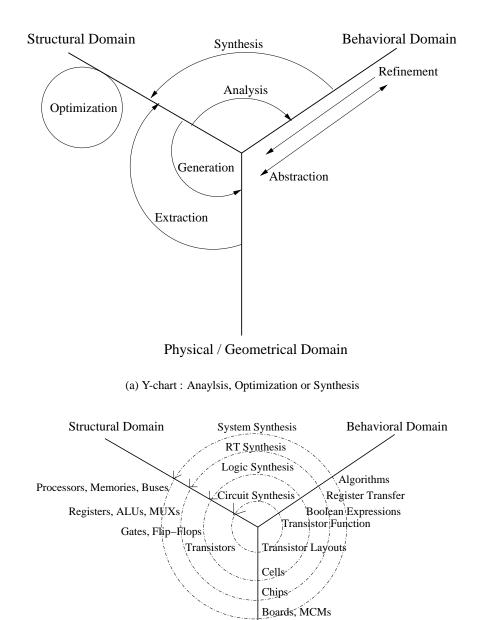

In circuit analysis, we study the behavior or characterisitcs of a circuit. Synthesis process is the reverse of analysis process. The task of synthesis process is to take the specifications of the behavior required for a system and a set of constraints and goals to be satisfied, and to find a structure that implements the behavior while satisfying the goals and constraints [3, 4, 15, 21]. The "behavior" of the system refers to the ways in which the system or its components interact with their environment (mapping from inputs to outputs). The "structure" refers to the set of interconnected components that constitute the system (described by a netlist). Finally, the structure must be mapped into a "physical" design. Behavior, structure and physical design are considered as three domains in which a hardware can be described (Fig. 1.2(a) and 1.2(b)). In behavioral domain, we are interested in what a design does, not in how it is built. The physical domain ingnores what the design is supposed to do and binds its structure in space or to silicon. A structual representation bridges the behavioral and physical representation. It is one-to-one mapping of a behavioral representation onto a set of components and connections under constraints, such as area, cost and delay.

Fig. 1.2(a) describes the design automation terminologies, such as optimization, synthesis, analysis, and optimization in the hardware representation domain. The axes in Y-chart (Fig. 1.2(b))

4

Physical / Geometrical Domain

(b) Y-chart : Detailed Hardware Description

Figure 1.2. Desription of Hardware in Different Domains and Abstractions [4]

Figure 1.3. Synthesis Flow

represent three different domains of description, such as behvaioral, structural and physical. Each concentric circle intersects the axes at a particular level of representation within a domain. It may be noted that the synthesis process is a transformation from the behavioral domain to the structual domain, which is represented as an arc in Fig. 1.2(a).

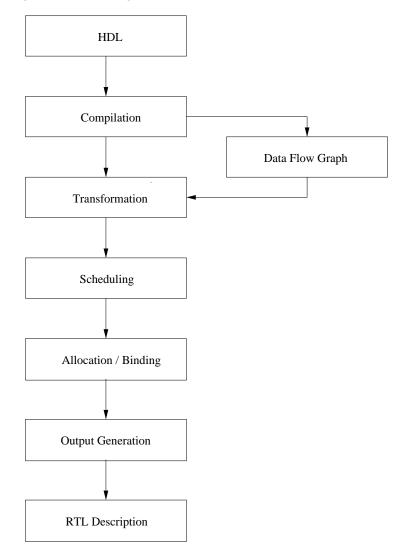

The digital circuits are designed and synthesised at several levels of abstraction as shown in Fig. 1.3.

• System Level: The system level is concerned with the overall system structure and information flow. Computer systems are described as interconnected set of processors, memories and switches in this level.

- Behavioral Level: This level is also called as Instruction Set Level or Algorithmic Level. At this level the focus is on the computations performed by an individual processor, the way it maps sequences of inputs to sequences of ouputs.

- Register Transfer Level: The system is viewed as a set of interconnected storage elements and functional blocks in this level. The behavior of system is described as a series of data transfers and transformations between the storage elements.

- Logic Level: Below the register transfer level is the logic level. The system is described as a network of gates and flip-flops and the behavior is specified by logic equations at this level.

- Layout Level: In this level, the system is specified in terms of the individual transistors of which it is composed. The behavior of the system can be described in terms of the network equations.

### 1.1.1 Why High-Level Synthesis ?

High-level synthesis is popular for the following reasons [3]:

- Shorter design cycle: If more of the design process is automated, faster products can be made available at cheaper prices.

- Fewer errors: Since the synthesis process can be verified easily, the chances of getting errors will be less.

- Ability to search the design space: As synthesis system can produce several designs in a small time, the designer has more flexibity to choose proper design considering different trade-offs.

- Documenting the design process: An automated system can keep track of design decisions and effect of those decisions.

- Availability of IC technology to more people: As design expertise is moved into synthesis system, it becomes easier for a non-expert to produce a chip that meets a given set of specifications.

#### 1.1.2 Various Phases of High-Level Synthesis

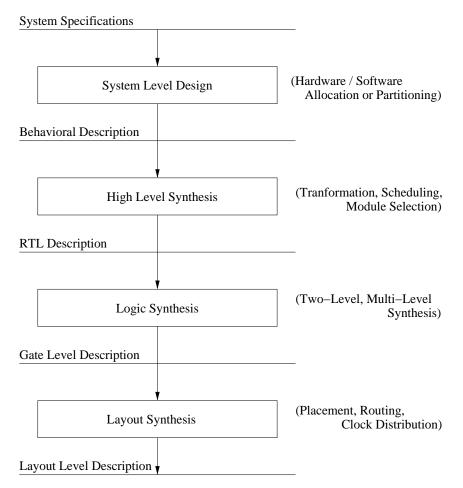

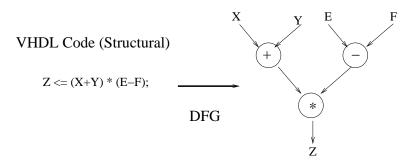

The various phases of high-level synthesis include, compilation, transformation, scheduling, allocation, binding as detailed in Fig. 1.4.

Figure 1.4. Various Phases of High-Level Synthesis

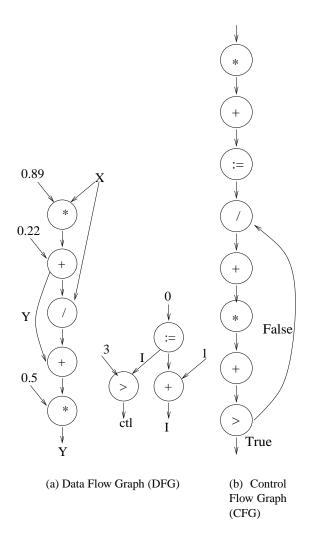

The behavior of a system to be synthesized is usually specified at the algorithmic level using a high-level programming language like Pascal, C or a hardware description language such as VHDL and Verilog [3, 22]. The behavior of the system is then compiled into internal representations, which are usually data flow graphs (DFGs) and control flow graphs (CFGs). Each behavioral specification is transformed into an unique graphical representation. The data flow graph is a

directed graph which represents the data moves, while the control flow graph is a directed graph which indicates the sequence of operations. The formal definitions of data flow graph and control flow are given below [3].

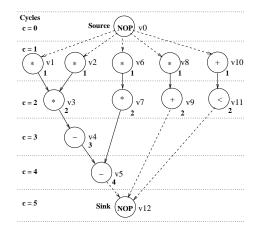

A data flow graph (DFG) is a directed graph G = (V, E), where: (i)  $V = v_1, v_2, ..., v_n$  is a finite set whose elements are "nodes", and (ii)  $E = V \times V$  is an asymmetric "data flow relation", whose elements are directed "data edges".

A control flow graph (CFG) is a directed graph G = (V, E), where: (i)  $V = v_1, v_2, ..., v_n$  is a finite set whose elements are "nodes", and (ii)  $E = V \times V$  is a "control flow relation", whose elements are directed "sequence edges".

Lets consider the following algorithm that computes the square root of X using Newton's method [3].

Algorithm : Square Root Calculations { Y := 0.22 + 0.89 \* X; I := 0;Do until I > 3 loop  $Y := 0.5 * (Y + \frac{X}{Y});$  I := I + 1;End do }

The above algorithm can be represented using the following data flow graph and control flow graph (Fig. 1.5).

In the transformation step, the initial data flow graph is transformed so that the resultant data flow graph is more suitable for scheduling and allocation. These transformations include compilerlike optimizations such as dead code elimination, common subexpression elimination, loop un-

Figure 1.5. Data Flow Graph and Control Flow Graph of a Square Root Algorithm [3]

rolling, constant propagation and code motion. In addition to this, some hardware-specific transformations like syntactic variances minimization, retiming may be applied to to take advantage of the associativity and commutativity of certain operations.

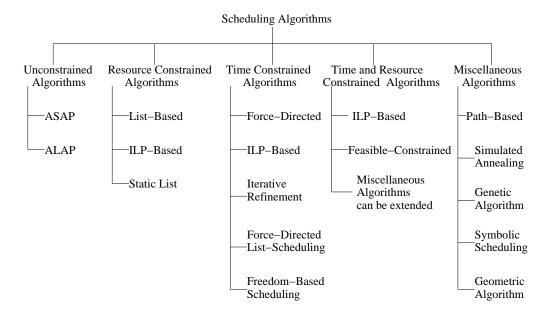

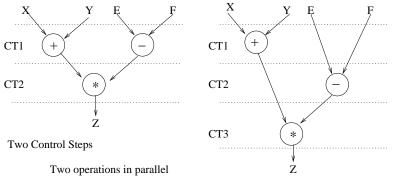

Scheduling is the process of partitioning the set of arithmetic and logical operations in the data flow graph into groups of operations so that the operations in the same group can be executed concurrently, while taking into consideration possible trade-offs between the total execution cost and hardware cost. A group of concurrent computations to be executed simultaneously is referred to as control step. The total number of control steps needed to execute all operations in the data

flow graph, the minimum number of functional units of each type to be used in the design, and the lifetimes of the variables generated during the computation of operations are determined in the scheduling step. Datapath scheduling algorithms may be of various types based on the constraints and optimization schemes as shown in Fig. 1.6. Various scheduling algorithms are described in [4, 21, 22, 3, 23, 24, 25, 26, 27, 28, 29, 30, 31, 32, 33, 2, 34, 35, 36, 37, 38]. The commonly used scheduling techniques are integer linear programming, as-soon-as possible, as-late-as possible, list-based scheduling, force directed scheduling and freedom-based scheduling, etc.

Figure 1.6. Different Types of Scheduling Algorithms

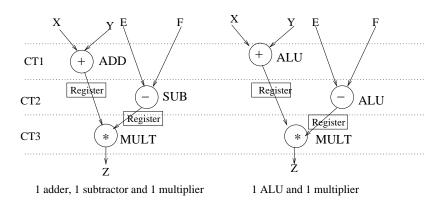

Allocation is the process of determining functional units of each type for performing operations, memory units(registers) for storing data values, and interconnects for data transportation. Binding is the process of assigning variables to memory units, and data transfers to interconnections. Allocation / binding is further divided into tasks, such as functional unit allocation / binding, memory unit allocation/binding and interconnect allocation / binding. The functional unit allocation / binding involves the mapping of operations in the behavioral description into a set of selected functional units. The memory unit allocation / binding maps data carriers(constants, variables, arrays) in the behavioral description onto storage elements(ROMs, registers, memory units) in the

datapath. The interconnect allocation / binding task maps every data transfer in the behavior into a set of interconnection units for data routing.

In the output generation phase, design output is generated. The output should be in a form, so that logic-level synthesis tools can optimize the combinational logic, and layout synthesis tools can design the chip geometry. The generated output is generally in a low level hardware description language, such as structural VHDL or EDIF [22].

#### **1.1.3** A Synthesis Example

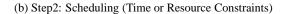

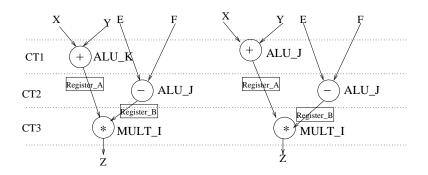

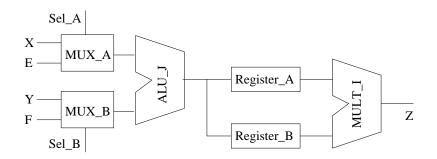

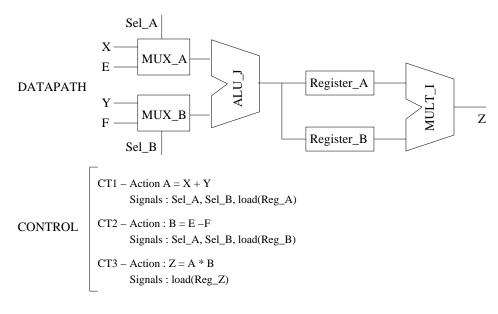

Let us consider a small synthesis example to learn the various phases of synthesis in detail. Suppose, we want to synthesize hardware to perform the operation : Z = (X + Y) \* (E - F). The following self explanatory Figs. (1.7 -1.8) illustrate the steps.

#### **1.2** Sources of Power Dissipation in a CMOS Circuit

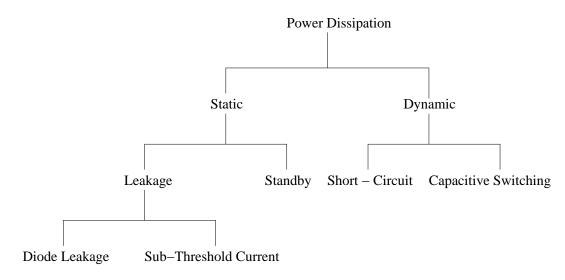

The details of power dissipations are shown in Fig. 1.9. Power dissipation in a CMOS circuit is caused by four sources [17] :

- Leakage current: It is determined by the fabrication process technology and consists of two components: (1) reverse bias current in the parasitic diodes formed between source and drain diffusions and the bulk region in the transistor, and (2) the subthreshold current that arises from the inversion charge that exists at the gate voltages below the threshold voltage.

- Standy current: It is the DC current drawn continuously form  $V_{dd}$  to ground.

- Short-circuit current: This is the current due to the DC path between the supply and ground during output transitions.

- Capacitance current: This curent flows to charge and discharge capacitance loads during logic changes.

Three Control Steps No parallel operation

(c) Step3: Allocation (Fixes Amount and Types of Resources)

Figure 1.7. A Synthesis Example : Step 1 to Step 3

(a) Step4: Binding (which Resource will be used by which Operation)

(b) Step5: Connection Allocation (Communication between Resources: Bus, Buffer or MUX)

(c) Step6: Architecture Generation (Datapath and Control)

Figure 1.8. The Synthesis Example : Step 4 to Step 6

Figure 1.9. Sources of Power Dissipation in a CMOS Circuit

*Capacitive switching power* dissipation is caused by charging and discharging of parasitic capacitance in the circuit and is given by Eqn. 1.1,

$$P_{dynamic} = \frac{1}{2}C_L V_{dd}^2 N f \tag{1.1}$$

where,  $C_L$  is load capacitor,  $V_{dd}$  is supply voltage, N is average or expected number of transitions per clock cycle (switching activity), and f is the clock frequency. During transition from either 0 to 1 or 1 to 0, both NMOS and PMOS are ON for a short period of time. Because of this there is flow of current from  $V_{dd}$  to  $V_{ss}$  (short current pulse). The power dissipation corresponding to this is called *short-circuit power* dissipation which is quantified as in Eqn. 1.2

$$P_{short} = \frac{\beta}{12} (V_{dd} - 2V_t)^3 \frac{t_{rf}}{t_p}$$

(1.2)

where,  $\beta$  is the transistor gain factor,  $V_{dd}$  is supply voltage,  $V_t$  is the threshold voltage,  $t_{rf}$  is the rise/fall time (under the assumption that  $t_r = t_f$ ) and  $t_p$  is the period of the input waveform. The *dynamic power dissipation* is the sum of the short-circuit and capacitative power dissipations.

The *leakage power* dissipation occurs because of reverse-biased diode (formed between diffusion regions and substrate) current and subthreshold current. Leakage currents in CMOS circuits

can be made small with the proper choice of device technology. Standby power dissipation happens when both the nMOS and pMOS transistors are continuously on in a psuedo-nMOS inverter, when the drain of an nMOS transistor is driving the gate of another nMOS transistor in a pass-transistor logic, or when the tristated input of a CMOS gate leaks away to a value between  $V_{dd}$  and ground. The *static-circuit power dissipation* is the sum of the leakage and standby power dissipations. The total static power of a CMOS circuit is obtained using the Eqn. 1.3 as given below (assuming *n* number of transistors). In practice, standby power is neglected compared to the leakage power and static power is assumed to be the leakage power.

$$P_{static} = \sum_{i=1}^{n} \text{leakage current * supply voltage}$$

=  $\sum_{i=1}^{n} (I_{\text{diode}} + I_{\text{subthreshold}}) * \text{supply voltage}$  (1.3)

#### 1.3 Methods for Power Reduction in High-Level Synthesis

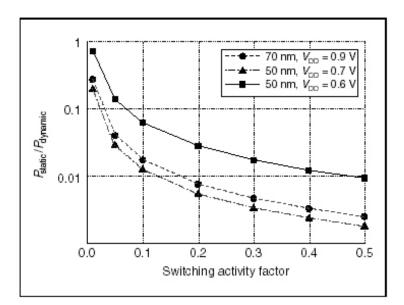

Leakage power dissipation is small in comparison to other components. In a well designed circuit, short-circuit power dissipation is less than 20% of dynamic power [39]. It is also evident from Fig. 1.10 [6, 7] that at larger switching activity the static power is negligible compared to the dynamic power dissipation. This shows that the dynamic power dissipation is the the main power dissipation that needs to be taken care of. From the dynamic power dissipation expression given in Eqn. 1.1, we can conclude that the parameters that can be varied to affect power as well as energy consumption are :

- supply voltage,

- the clock frequency,

- the switching activity per clock cycle at various signals in the circuit,

- the parasitic capacitance.

It is important to note that these parameters are not independent. It is necessary to take into account the interactions and trade-offs among these parameters to minimize power consumption [17]. The key principles used for low-power design are as follows [20, 40] :

Figure 1.10. Static Vs Dynamic Power Dissipation for Different Switching Activity [6, 7]

- using the lowest possible supply voltage

- using the smallest geometry, highest frequency devices, but operating them at lowest possible frequency,

- using parallelism and pipelining to lower required frequency of operation,

- power management by disconnecting the power source when the system is idle, and

- designing systems to have lowest requirements on subsystem performance for the given level functionality.

Based on the above observations, following are the some techniques used to reduce power consumption in high-level synthesis [41, 22, 1, 9, 42, 40].

• Transformation: The basic approach is to scan the design space by utilizing various flow graph transformations with high-level power estimation techniques, and transform data flow graphs into less power consuming data flow graphs.

- Operator shutdown: The massive switching in large components, such as adders, multipliers and registers, consume a large amount of power. By disabling the clock signal the internal nodes remain at static voltage levels and do not consume power.

- Lower supply voltages: In a CMOS circuit, power consumption decreases quadratically with voltage while the speed reduction is linear. When intensive computation is not needed, the supply voltage is lowered and consequently can save power consumption.

- Mixed voltage circuit: Dual voltages on one IC are attractive enough for commercial consideration. Although such an approach is viable, designers must carefully consider cross-talk and latch-up issues among others.

- Increased parallelism: Slower operations can be used on non-time critical paths, while parallelism can be increased to compensate for slower components. The parallel option consumes less power and has a shorter total delay. However, extra area might be needed to achieve the parallelism.

#### 1.4 Why Peak Power Minimization ?

With the increase in chip densities and clock frequencies the demand for design of low power integrated circuits has increased. The literature is rich on efforts to reduce total energy consumption and average power consumption of the CMOS circuits. At the same time, the reduction of peak power consumption is essential for the following reasons [43, 5, 8, 44, 45, 46] :

- to maintain supply voltage levels,

- to increase reliability and

- smaller heat sinks and cheaper packaging.

The peak power is the maximum power consumption of the integrated circuit (IC) at any instance during its execution. If the current flow is large, then the IR drop of the interconnects becomes large which can reduce the supply voltage levels at different parts of a IC. High current flow can

reduce reliability because of hot electron effects and high current density. The hot electron effects may lead to runaway current failures and electrostatic discharge failures. High current density can cause electromigration failure. It is observed that the mean time to failure (MTF) of CMOS circuit is inversely proportional to current density (or power density). If the current (power) dissipation is large, then the heat generated out of the system is large. This in turn, needs bigger sink and costlier heat dissipation mechanism in order to maintain the operating temperature of the ICs in its tolerance limit.

### 1.5 Why Average Power and Energy Reduction ?

Energy and average power reduction is essential for the following reasons [17, 8, 5, 46]:

- to increase battery life time,

- to enhance noise margin,

- to reduce cooling and energy costs,

- to reduce use of natural resources, and

- to increase system reliability.

The battery life time is determined by the Ah (ampere hour) rating of the battery. If the average power (and/or energy) consumption is high, then battery life time may reduce because of high ampere consumption. This factor is important for portable applications. The reduction of average power is essential to enhance noise margin (to decrease functional failure). The cost of packaging and cooling is determined by average current flow and hence, the average power and energy. The high energy consumption of the computer systems leads to environment concerns due to the need for more power generation. If the average power is large, the operating temperature of the chip increases, which may lead to failures. It is estimated that for each  $10^{\circ}C$  increase in the operating temperature, the failure rates of the components is roughly doubled.

#### 1.6 Why Transient Power Minimization ?

Both the peak power and peak power differential describe the transient power characteristics of a CMOS circuit. In the above section we discussed the needs for peak power reduction. The peak power differential needs to be reduced for the following reasons [8, 5, 47, 48]:

- to reduce power supply noise,

- to reduce cross talk and electromagnetic noise,

- to increase battery efficiency and

- to increase reliability.

Power fluctuation leads to larger  $\frac{di}{dt}$  causing power supply noise, (similar to *IR* drop), because of self inductance of power supply lines. Crosstalk is the noise voltage induced in signal line due to the switching in another signal line [5]. The voltage induced by the mutual inductance is expressed as  $L\frac{di}{dt}$  and that induced by the mutual capacitance as  $C\frac{dv}{dt}$ . If the power fluctuation is high, then large  $\frac{di}{dt}$  and  $\frac{dv}{dt}$  can introduce significant noise in the signal lines. As the power fluctuation increases, it reduces the electrochemical conversion and hence there is decrease in battery life [49]. High current peaks (power fluctuation) in short time spans can cause high heat dissipation in a localised area of silicon die which may lead to permanent failure of the integrated circuit.

# 1.7 Why Frequency and Voltage Scaling ?

With the increasing demand for portable electronic devices, power reduction has emerged as a major design goal in VLSI circuits. Let us consider the following equations for a CMOS circuit [50, 51, 52, 53, 54, 55, 56] :

• Energy dissipation per operation is

$$E_{dynamic} = C_{eff} V_{dd}^2 \tag{1.4}$$

where,  $C_{eff}$  is the effective switched capacitance and  $V_{dd}$  is the supply voltage,

• Power dissipation for the operation is

$$P_{dynamic} = C_{eff} V_{dd}^2 f \tag{1.5}$$

where, f is the frequency.

• Further, the critical delay  $(t_d)$  in a device that determines the maximum frequency  $(f_{max})$  is

$$t_d = k \frac{V_{dd}}{(V_{dd} - V_t)^{\alpha}} \tag{1.6}$$

where,  $V_T$  is the threshold voltage,  $\alpha$  is a technology dependent factor and k is a constant. From the above three equations, the following can be deduced [50, 52, 57, 9, 54, 55, 58]:

- By reducing only  $V_{dd}$ , both energy and power can be saved at the cost of performance (speed / time).

- Slowing down CPU by reducing only f will save power but not energy.

- However, by scaling frequency and voltage in a coordinated manner, both energy and power can be saved while maintaining performance.

The third factor above forms the major motivation for this work. The objective is to generate a datapath schedule that attempt at energy and power reduction without degrading the performance by using multiple voltages and dynamic frequency clocking in a co-ordinated manner. Moreover, simultaneous voltage and frequency reduction opens oppurtunity for power reduction in three folds. In this dissertation, we investigate the power and energy reduction due to combined use of multiple supply voltages, dynamic frequency clocking, and multicycling.

### 1.8 Multiple Supply Voltages, Dynamic Clocking and Multicycling Preliminaries

In Section 1.7, we have seen that voltage and frequency need to be varied in a co-ordinated manner to get better results in terms of power, energy or performance. Dynamic frequency clocking is a mechanism to vary clock frequency on the fly depending on the computation. In multiple supply

voltage scheme, different modules or functional units are operated at different supply voltages. Similarly, variable voltage scheme is a technique in which the operating voltage is valid from time to time. This chapter discusses how energy and power reduction can be achieved through the use of dynamic frequency clocking, voltage scaling multicyling. Further, the design related issues of having multiple supply voltages in a processor are discussed. Design of level converters and dynamic frequency clocking units are also presented.

#### 1.8.1 What is Dynamic Frequency Clocking?

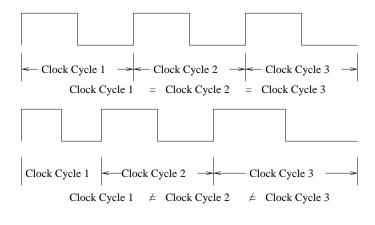

In dynamic frequency clocking, the functional units can be operated at different frequencies depending on the computations occuring within the datapath during a given clock cycle. The strategy is to schedule high energy units, such as multipliers at lower frequencies such that they can be operated at lower voltages to reduce energy consumption and the low energy units, such as adders at higher frequencies, to compensate for speed. In this clocking scheme, all the units are clocked by a single clock line which switches at run-time. A clocking mechanism that varies the clock frequency dynamically has been shown to improve the execution time as compared to using a uni-frequency global clock [59]. Generation of such types of clocks have been studied extensively in [60, 61, 62, 63]. Fig. 1.11(a) shows the uni-frequency and dynamic frequency diagrams.

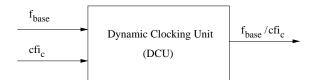

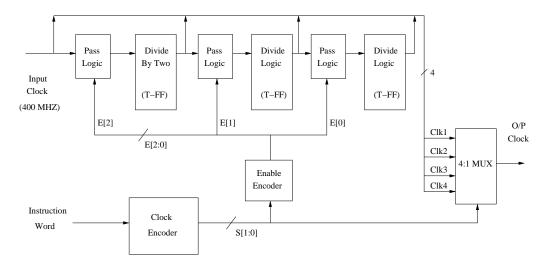

The dynamic clocking unit (DCU) which generates the required clock frequency uses a clock divider strategy to generate frequency which are submultiples of the base frequency. Base frequency  $f_{base}$  is the maximum frequency (or multiple of maximum) of any functional unit (FU) at the maximum supply voltage. A value  $cfi_c$  (cycle frequency index for control step c) is loaded as an input to the DCU which comes from controller. The scheme for dynamic frequency generation is shown in Fig. 1.11(b). Loading a value of  $cfi_c$  into the counters provide a divided output clock of frequency  $\frac{f_{base}}{cfi_c}$ .

# 1.8.2 Energy or Power Reduction Due to Voltage or Frequency Scaling

To understand how multiple supply voltage, variable frequency and multicycling can be helpful in energy or power reductions, let us consider the small data flow graph shown in Fig. 1.12(a).

(a) Single Frequency Vs Dynamic Frequency

(b) Dynamic Frequency Generation

Figure 1.11. Dynamic Frequency Generation using Dynamic Clocking Unit [54]

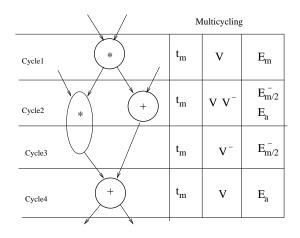

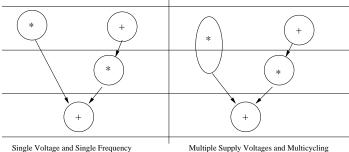

Let us analyse the power, energy consumption for this data flow graph in three possible modes of datapath operation, such as (i) single supply voltage and single frequency, (ii) multiple supply voltage and variable or dynamic frequency, and (iii) multiple supply voltage and multicycling [54, 55, 64]. Let  $t_a$  and  $t_m$  be the delays of the adder and the multiplier respectively at the maximum supply voltage V. The DFG is scheduled to three control steps.

Single supply voltage and single frequency (SVSF): Each cycle has clock width determined by the slowest operator delay  $t_m$ . The total energy consumption is given by  $E_{sf} = 2E_m + 2E_a$  and the total delay is  $T_{sf} = 3t_m$ . In this case, the peak power consumption is given by,  $P_{peak,sf} = \frac{E_m + E_a}{t_m}$ . Multiple supply voltages and dynamic frequency (MVDFC): Let,  $E_m^-$  and  $E_a^-$  are some energy values less than  $E_m$  and  $E_a$  respectively and  $t_m^+$  be the delay of the multiplier at lower voltage  $V^-$ . In data flow graph shown in Fig. 1.12(a), assuming that, the clock cycle width for the  $3^{\text{rd}}$  cycle is  $t_a$  which is smaller than  $t_m$ . This allows us to increase the clock width of some other cycles from  $t_m$  to some  $t_m^+$  without violating the time constraints (or without time penalty). In this case, the total

|        | $\langle \rangle$ | Single Frequency |     | Dynamic Frequency                |                |    |                                  |

|--------|-------------------|------------------|-----|----------------------------------|----------------|----|----------------------------------|

| Cycle1 | *                 | t <sub>m</sub>   | v   | Em                               | $t_m^+$        | v  | $E_m^-$                          |

| Cycle2 | * +               | t <sub>m</sub>   | v v | E <sub>m</sub><br>E <sub>a</sub> | t <sub>m</sub> | vv | E <sub>m</sub><br>E <sub>a</sub> |

| Cycle3 | +                 | t <sub>m</sub>   | V   | E <sub>a</sub>                   | t <sub>a</sub> | v  | Ea                               |

|        |                   |                  |     |                                  |                |    |                                  |

(a) Data Flow Graph : Variable Frequency Vs Single Frequency

(b) Data Flow Graph : Multicycling  $\rightarrow$  Performance Degradation

Multiple Supply Voltages and Multicycling

(c) Data Flow Graph : Multicycling  $\rightarrow$  No Performance Degradation

Figure 1.12. Data Flow Graph in Three Modes of Operation

delay  $T_{dfc} = t_m^+ + t_m + t_a$  and the energy consumption is given by  $E_{dfc} = E_m + E_a + E_m^- + E_a^-$ . Since,  $T_{dfc} \approx T_{sf}$  and  $E_{dfc} < E_{sf}$ , energy reduction is achieved without degrading performance. Energy overhead of level converters have to be considered for this case. The peak power consumption is given by,  $P_{peak,dfc} = \frac{E_m + E_a^-}{t_m}$ .

Multiple supply voltages and multicycling (MVMC) : In this mode of operation, the functional units are operated at multiple supply voltages. The functional units operating at low voltage are made to run in more than one consecutive control steps. Let us assume that multiplier takes two control steps, when it is operated at a lower supply voltage. The example data flowgraph for the multicycling case in shown in Fig. 1.12(b). In this case, the total energy consumption  $E_{mc} = E_m + E_m^- + 2E_a$  and total delay  $T_{mc} = 4t_m$ . Since,  $T_{mc} > T_{sf}$  and  $E_{mc} < E_{sf}$ , energy reduction is obtained with a degradation in performance of the circuit. For the multicycling case, level converters are the only overheads. The peak power consumption of the DFG will be determined by the multiplication operation in control step 1,  $P_{peak,mc} = \frac{E_m}{t_m}$ . This is based on the observation that the power consumption of the multipliers are much higher than that of the adders. It may be noted the above mentioned performance degradation may not always happen. For example, consider a DFG such as the one shown in Fig. 1.12(c); although the multiplier is scheduled in two control steps there is no change is the critical path delay. The delay is  $3t_m$  for both SVSF and MVMC cases.

### **1.8.3** Issues in Multiple Supply Voltage Based Design

A designer needs to take into consideration several design issues when a multiple voltage design is targeted for fabrication. The effects of multiple voltage operation on IC layout and power supply requirements should be considered [65, 66, 67]. Multiple voltage design may affect IC design in the following ways :

• If the multiple supplies are generated off-chip, additional power and ground pins will be required.

- It may be necessary to partition the chip into separate regions, where all modules in a region operate at the same voltage.

- Some kind of isolation will be required between the regions operated at different voltages.

- There may be some limit on the voltage difference that can be tolerated between the regions.

- Protection against latch-up may be needed at the logic interfaces between regions of different voltages.

- New design rules for routing may be needed to deal with signals at one voltage passing through a region at another voltage.

- Choice between generating the voltage on-chip or off-chip has to be made depending on the application.

- Clocking scheme needs to be modified.

# **1.8.4** Level Converter Design

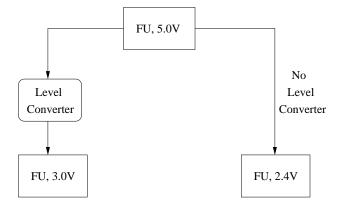

We already know that whenever one resource has to drive an input of another resource operating at a different voltage, a level conversion is needed. Thus, level-converter or level-shifter is the most essential component for multiple supply voltage designs. This results in overheads in the form of area and power for multiple supply voltage designs as compared to single supply voltage designs. Four possible alternatives are used by various researchers as listed below [65].

- The level conveters can be omitted.

- A chain of inverters can be used at successive higher voltages.

- An active or passive pullup can be used.

- A differential cascode voltage switch (DVCS) can be used.

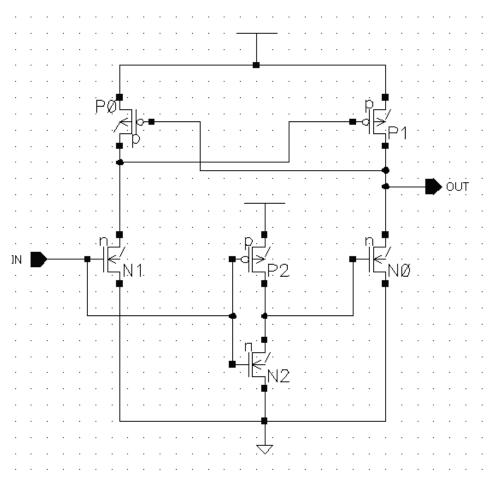

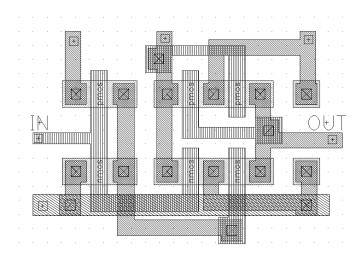

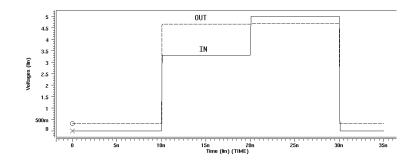

Various level converter designs have been discussed in [66, 68, 69, 67, 65]. We implemented the level converter design proposed in [65, 66] to get better understanding. The schematic diagram,

Figure 1.13. Level Converter Schematic Diagram [65, 66]

the layout and the simulation waveform is given in Fig. 1.13, 1.14(a) and 1.14(b) respectively. The constant output voltage indicates that the level converter can step up or step down the voltage to produce a constant supply voltage.

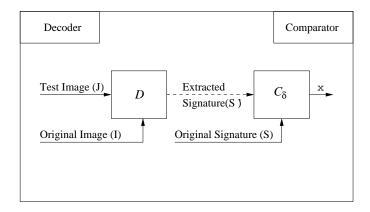

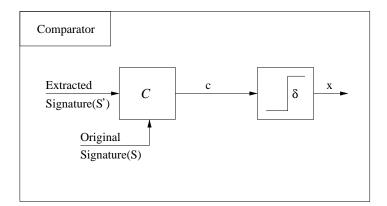

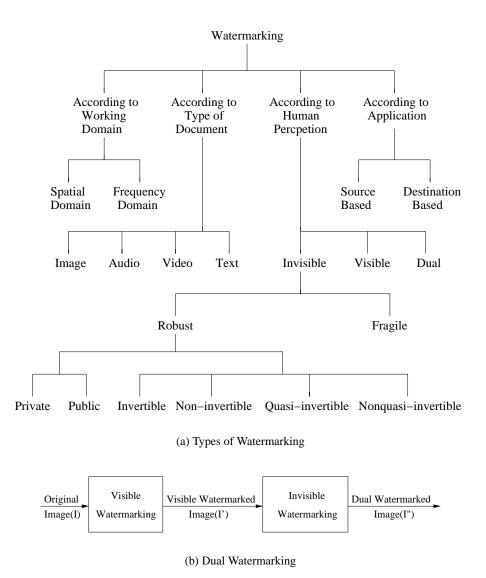

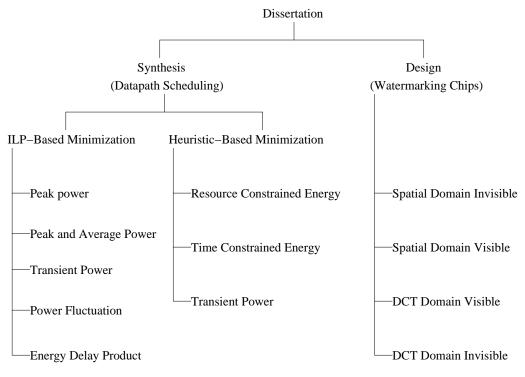

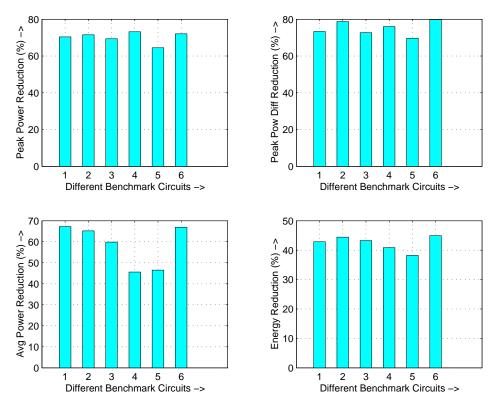

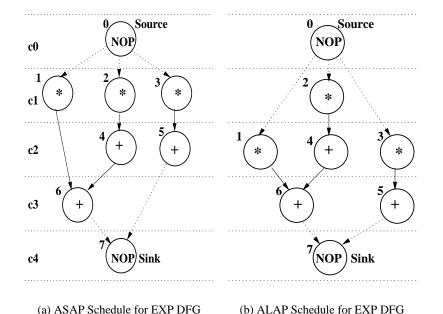

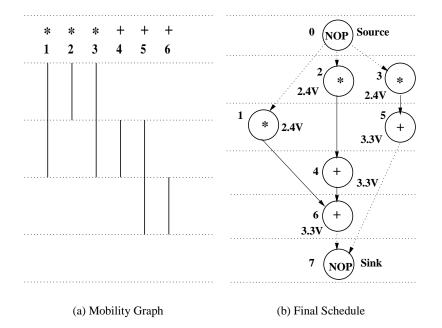

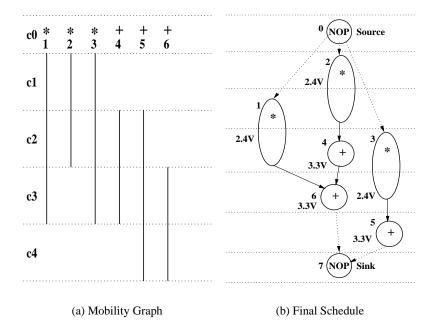

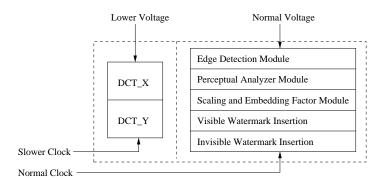

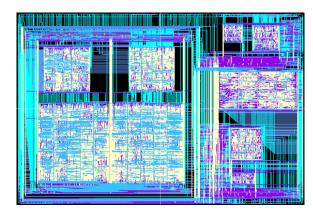

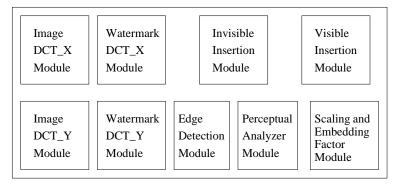

# 1.8.5 Dynamic Frequency Clocking Unit Design